## IEEE® 802.11 b/g/n Network Controller Module with Integrated Bluetooth® Low Energy 4.0

### Introduction

The ATWINC3400-MR210CA is an IEEE 802.11 b/g/n RF/Baseband/Medium Access Control (MAC) network controller module with Bluetooth Low Energy technology that is compliant with Bluetooth version 4.0. This module is optimized for low power and high performance mobile applications. This module features small form factor when integrating Power Amplifier (PA), Low-Noise Amplifier (LNA), Transmit/ Receive (T/R) switch (for Wi-Fi<sup>®</sup> and Bluetooth), Power Management Unit (PMU), and Chip Antenna. The ATWINC3400-MR210CA module requires a 32.768 kHz clock for Sleep operation.

The ATWINC3400-MR210CA module utilizes highly optimized IEEE 802.11 Bluetooth coexistence protocols, and provides Serial Peripheral Interface (SPI) to interface with the host controller.

### Features

#### Wi-Fi features:

- IEEE 802.11 b/g/n RF/PHY/MAC

- IEEE 802.11 b/g/n (1x1) with single spatial stream, up to 72 Mbps PHY rate in 2.4 GHz ISM band

- Integrated chip antenna

- · Superior sensitivity and range via advanced PHY signal processing

- Advanced equalization and channel estimation

- Advanced carrier and timing synchronization

- Supports Soft-AP

- Supports IEEE 802.11 WEP, WPA, and WPA2

- Superior MAC throughput through hardware accelerated two-level A-MSDU/A-MPDU frame aggregation and block acknowledgment

- On-chip memory management engine to reduce the host load

- Operating temperature range from -40°C to +85°C

- Wi-Fi Alliance<sup>®</sup> certified for connectivity and optimizations

#### - ID: WFA62065

- Integrated on-chip microcontroller

- SPI host interface

- Integrated Flash memory for Wi-Fi and Bluetooth system software

- Low leakage on-chip memory for state variables

- Fast AP re-association (150 ms)

- On-chip network stack to offload MCU

- Integrated network IP slack to minimize the host CPU requirements

Network features: Firmware version 1:2:x

TCP, UDP, DHCP, ARP, HTTP, SSL, DNS, and SNTP

#### Bluetooth features:

- Bluetooth 4.0 (Bluetooth Low Energy) certifications

- Controller QD ID 77870

- Host QD ID 77451

- Adaptive Frequency Hopping (AFH)

- Superior sensitivity and range

## **Table of Contents**

| Intr | oduct                                                                                          | ion                                                                                                                                                                                | 1                    |

|------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Fea  | atures                                                                                         | 5                                                                                                                                                                                  | 1                    |

| 1.   | Orde                                                                                           | ring Information and Module Marking                                                                                                                                                | 5                    |

| 2.   | Block                                                                                          | c Diagram                                                                                                                                                                          | 6                    |

| 3.   | Pinou<br>3.1.                                                                                  | ut and Package Information                                                                                                                                                         |                      |

| 4.   | Elect                                                                                          | rical Characteristics1                                                                                                                                                             | 1                    |

|      | <ol> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> </ol> | Absolute Maximum Ratings<br>Recommended Operating Conditions<br>DC Characteristics<br>IEEE 802.11 b/g/n Radio Performance<br>Bluetooth Radio Performance<br>Timing Characteristics | 11<br>12<br>12<br>14 |

| 5.   | Powe                                                                                           | er Management                                                                                                                                                                      | 21                   |

|      | 5.1.<br>5.2.<br>5.3.<br>5.4.                                                                   | Device States                                                                                                                                                                      | 21<br>21<br>22       |

| 6.   | Cloc                                                                                           | king2                                                                                                                                                                              | 24                   |

|      | 6.1.                                                                                           | Low-Power Clock                                                                                                                                                                    | 24                   |

| 7.   | CPU<br>7.1.<br>7.2.<br>7.3.                                                                    | and Memory Subsystem.       2         Processor.       2         Memory Subsystem.       2         Nonvolatile Memory.       2                                                     | 25<br>25             |

| 8.   | WLA                                                                                            | N Subsystem                                                                                                                                                                        | 27                   |

|      | 8.1.<br>8.2.<br>8.3.                                                                           | MAC                                                                                                                                                                                | 28                   |

| 9.   | Bluet                                                                                          | tooth Low Energy 4.0                                                                                                                                                               | 0                    |

| 10.  | 10.1.<br>10.2.                                                                                 | rnal Interfaces                                                                                                                                                                    | 31<br>32             |

| 11. Application Reference Design              | 36 |

|-----------------------------------------------|----|

| 11.1. Host Interface - SPI                    | 36 |

| 12. Module Outline Drawings                   | 38 |

| 13. Design Consideration                      | 39 |

| 13.1. Module Placement and Routing Guidelines | 39 |

| 13.2. Antenna Performance                     | 40 |

| 14. Reflow Profile Information                | 42 |

| 14.1. Storage Condition                       | 42 |

| 14.2. Solder Paste                            |    |

| 14.3. Stencil Design                          |    |

| 14.4. Baking Conditions                       |    |

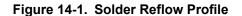

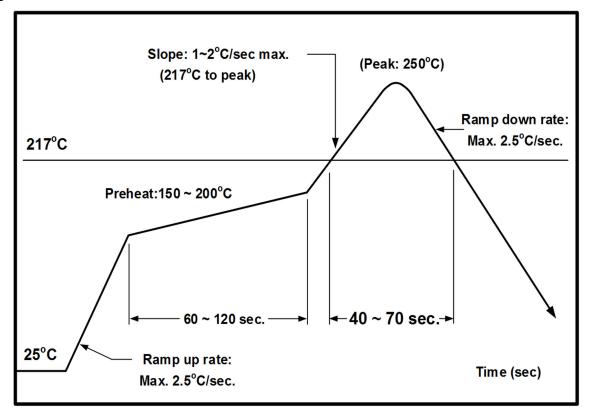

| 14.5. Soldering and Reflow Condition          | 42 |

| 15. Module Assembly Considerations            | 45 |

| 16. Regulatory Approval                       | 46 |

| 16.1. United States                           | 46 |

| 16.2. Canada                                  | 47 |

| 16.3. Europe                                  |    |

| 16.4. Other Regulatory Information            | 50 |

| 17. Reference Documentation                   | 51 |

| 18. Document Revision History                 | 52 |

| The Microchip Web Site                        | 53 |

| Customer Change Notification Service          | 53 |

| Customer Support                              | 53 |

| Microchip Devices Code Protection Feature     | 53 |

| Legal Notice                                  | 54 |

| Trademarks                                    | 54 |

| Quality Management System Certified by DNV    | 55 |

| Worldwide Sales and Sanvies                   | 56 |

| Worldwide Sales and Service                   | oc |

## 1. Ordering Information and Module Marking

The following table provides the ordering details for the ATWINC3400-MR210CA module.

#### Table 1-1. Ordering Details

| Model Number           | Ordering Code              | Package                      | Description                              | Regulatory<br>Information |

|------------------------|----------------------------|------------------------------|------------------------------------------|---------------------------|

| ATWINC3400-<br>MR210CA | ATWINC3400-MR210CAxxx<br>1 | 22.43 x<br>14.73 x 2.0<br>mm | Certified<br>module with<br>chip antenna | FCC, IC, CE               |

#### Note:

'xxx' in the preceding table and following figure denotes the software version. For example, at the time of publish the software is v1.22, so its equivalent order code is ATWINC3400-MR210CA122. The order code changes as per the software version. For more information on ordering code, refer to the ATWINC3400-MR product page.

The following figure illustrates the ATWINC3400-MR210CA module marking information.

#### Figure 1-1. Marking Information

|                     | ATWINC3400 | MR | 2     | 1     | 0           | С         | А         | xxx         |

|---------------------|------------|----|-------|-------|-------------|-----------|-----------|-------------|

|                     |            |    |       |       | <br> <br>   |           |           |             |

| Device name         |            |    |       |       |             |           |           |             |

| MR: Industrial      |            | I  |       |       |             | <br> <br> |           |             |

| 2: OTA with shield  |            |    | <br>! |       | I<br>I<br>I | I<br>I    |           |             |

| 1: Reserved         |            |    |       | '<br> |             |           |           |             |

| 0: Reserved         |            |    |       |       | '           |           |           |             |

| C: Chip antenna <   |            |    |       |       |             | J         | <br> <br> | 1<br>1<br>1 |

| Revision letter 🛛 🗲 |            |    |       |       |             |           | '         |             |

| Software version    |            |    |       |       |             |           |           | '           |

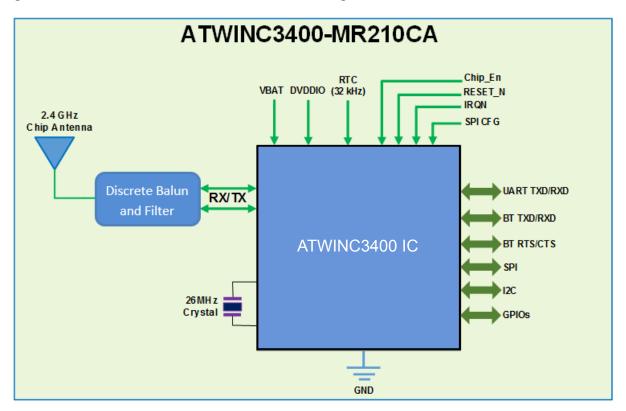

## 2. Block Diagram

The following figure shows the block diagram of the ATWINC3400-MR210CA module. **Figure 2-1. ATWINC3400-MR210CA Module Block Diagram**

**Pinout and Package Information**

## 3. Pinout and Package Information

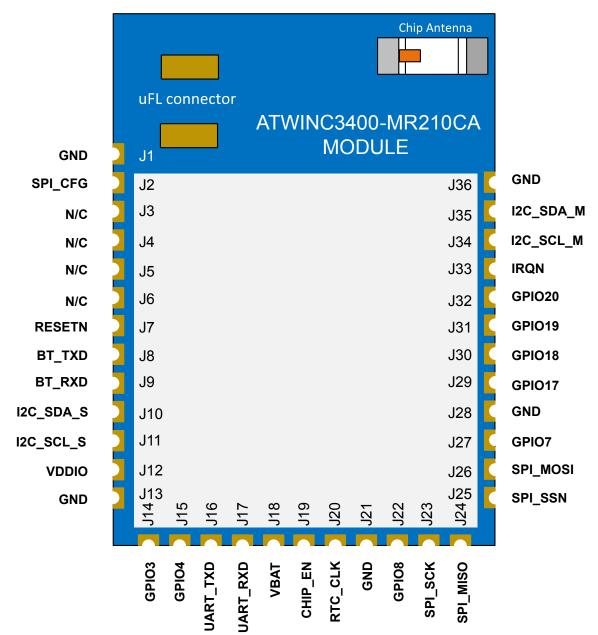

This package contains an exposed paddle that must be connected to the system board ground. The ATWINC3400-MR210CA module pin assignment is shown in following figure.

Figure 3-1. ATWINC3400-MR210CA Module Pin Assignment

The following table provides the ATWINC3400-MR210CA module pin description.

Pinout and Package Information

| Pin # | Pin Name  | Pin Type                             | Description                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-----------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GND       | GND                                  | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                |

| 2     | SPI_CFG   | Digital Input                        | Serial Peripheral Interface pin, which must be tied to VDDIO.                                                                                                                                                                                                                                                                                                                              |

| 3     | NC        | -                                    | No connection.                                                                                                                                                                                                                                                                                                                                                                             |

| 4     | NC        | -                                    | No connection.                                                                                                                                                                                                                                                                                                                                                                             |

| 5     | NC        | -                                    | No connection.                                                                                                                                                                                                                                                                                                                                                                             |

| 6     | NC        | -                                    | No connection.                                                                                                                                                                                                                                                                                                                                                                             |

| 7     | RESETN    | Digital Input                        | <ul> <li>Active-low hard Reset pin.</li> <li>When the Reset pin is asserted low, the module is in the Reset state. When the Reset pin is asserted high, the module functions normally.</li> <li>This pin must connect to a host output that is low by default on power-up. If the host output is tri-stated, add a 1 MOhm pull down resistor to ensure a low level at power-up.</li> </ul> |

| 8     | BT_TXD    | Digital I/O,<br>Programmable pull up | Bluetooth UART transmit data output pin.                                                                                                                                                                                                                                                                                                                                                   |

| 9     | BT_RXD    | Digital I/O,<br>Programmable pull up | Bluetooth UART receive data input pin.                                                                                                                                                                                                                                                                                                                                                     |

| 10    | I2C_SDA_S | Digital I/O,<br>Programmable pull up | <ul> <li>I2C Slave data pin.</li> <li>Used only for test purposes. It is recommended to add a test point for this pin.</li> </ul>                                                                                                                                                                                                                                                          |

| 11    | I2C_SCL_S | Digital I/O,<br>Programmable pull up | <ul> <li>I2C Slave clock pin.</li> <li>Used only for test purposes. It is recommended to add a test point for this pin.</li> </ul>                                                                                                                                                                                                                                                         |

| 12    | VDDIO     | Power                                | Digital I/O power supply.                                                                                                                                                                                                                                                                                                                                                                  |

| 13    | GND       | GND                                  | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                |

| 14    | GPIO3     | Digital I/O,<br>Programmable pull up | General Purpose Input/Output pin.                                                                                                                                                                                                                                                                                                                                                          |

| 15    | GPIO4     | Digital I/O,<br>Programmable pull up | General Purpose Input/Output pin.                                                                                                                                                                                                                                                                                                                                                          |

| 16    | UART_TXD  | Digital I/O,<br>Programmable pull up | Wi-Fi UART TxD output pin.                                                                                                                                                                                                                                                                                                                                                                 |

#### Table 3-1. ATWINC3400-MR210CA Module Pin Description

## Pinout and Package Information

| Pin # | Pin Name | Pin Type                             | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|----------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |          |                                      | <ul> <li>Used only for debug development<br/>purposes. It is recommended to add a<br/>test point for this pin.</li> </ul>                                                                                                                                                                                                                                                                   |

| 17    | UART_RXD | Digital I/O,<br>Programmable pull up | <ul> <li>Wi-Fi UART RxD input pin.</li> <li>Used only for debug development<br/>purposes. It is recommended to add a<br/>test point for this pin.</li> </ul>                                                                                                                                                                                                                                |

| 18    | VBAT     | Power                                | Power supply pin for DC/DC converter and PA.                                                                                                                                                                                                                                                                                                                                                |

| 19    | CHIP_EN  | Digital Input                        | <ul> <li>PMU enable pin.</li> <li>When the CHIP_EN pin is asserted high, the module is enbled. When the CHIP_EN pin is asserted low, the module is disabled or put into Power-Down mode.</li> <li>Connect to a host output that is low by default at power-up. If the host output is tri-stated, add a 1 MOhm pull down resistor if necessary to ensure a low level at power-up.</li> </ul> |

| 20    | RTC_CLK  | Digital I/O,<br>Programmable pull up | <ul> <li>RTC Clock input pin.</li> <li>This pin must connect to a 32.768 kHz clock source.</li> </ul>                                                                                                                                                                                                                                                                                       |

| 21    | GND      | GND                                  | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                 |

| 22    | GPIO8    | Digital I/O,<br>Programmable pull up | General Purpose Input/Output pin.                                                                                                                                                                                                                                                                                                                                                           |

| 23    | SPI_SCK  | Digital I/O,<br>Programmable pull up | SPI clock pin.                                                                                                                                                                                                                                                                                                                                                                              |

| 24    | SPI_MISO | Digital I/O,<br>Programmable pull up | SPI MISO (Master In Slave Out) pin.                                                                                                                                                                                                                                                                                                                                                         |

| 25    | SPI_SSN  | Digital I/O,<br>Programmable pull up | Active-low SPI SSN (Slave Select) pin.                                                                                                                                                                                                                                                                                                                                                      |

| 26    | SPI_MOSI | Digital I/O,<br>Programmable pull up | SPI MOSI (Master Out Slave In) pin.                                                                                                                                                                                                                                                                                                                                                         |

| 27    | GPIO7    | Digital I/O,<br>Programmable pull up | General Purpose Input/Output pin.                                                                                                                                                                                                                                                                                                                                                           |

| 28    | GND      | GND                                  | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                 |

| 29    | GPIO17   | Digital I/O,<br>Programmable pull up | General Purpose Input/Output pin.                                                                                                                                                                                                                                                                                                                                                           |

| 30    | GPIO18   | Digital I/O,<br>Programmable pull up | General Purpose Input/Output pin.                                                                                                                                                                                                                                                                                                                                                           |

#### **Pinout and Package Information**

| Pin # | Pin Name   | Pin Type                                | Description                                                                                                                                      |

|-------|------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | GPIO19     | Digital I/O,<br>Programmable pull up    | General Purpose Input/Output pin.                                                                                                                |

| 32    | GPIO20     | Digital I/O,<br>Programmable pull up    | General Purpose Input/Output pin.                                                                                                                |

| 33    | IRQN       | Digital output,<br>Programmable pull up | <ul> <li>ATWINC3400-MR210CA module host<br/>interrupt request output pin.</li> <li>This pin must connect to a host interrupt<br/>pin.</li> </ul> |

| 34    | I2C_SCL_M  | Digital I/O,<br>Programmable pull up    | I2C Master clock pin.                                                                                                                            |

| 35    | I2C_SDA_M  | Digital I/O,<br>Programmable pull up    | I2C Master data pin.                                                                                                                             |

| 36    | GND        | GND                                     | Ground pin.                                                                                                                                      |

| 37    | PADDLE VSS | Power                                   | Connect to system board ground.                                                                                                                  |

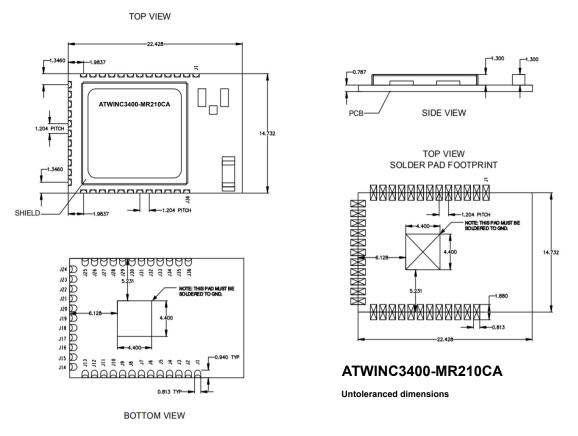

### 3.1 Package Description

The following table provides the ATWINC3400-MR210CA module package dimensions.

#### Table 3-2. ATWINC3400-MR210CA Module Package Information

| Parameter        | Value         | Unit |

|------------------|---------------|------|

| Pad count        | 36            | -    |

| Package size     | 22.43 x 14.73 | mm   |

| Total thickness  | 2.09          |      |

| Pad pitch        | 1.20          |      |

| Pad width        | 0.81          |      |

| Exposed pad size | 4.4 x 4.4     |      |

#### **Electrical Characteristics**

## 4. Electrical Characteristics

This chapter provides an overview of the electrical characteristics of the ATWINC3400-MR210CA module.

### 4.1 Absolute Maximum Ratings

The following table provides the absolute maximum ratings for the ATWINC3400-MR210CA module.

Table 4-1. ATWINC3400-MR210CA Module Absolute Maximum Ratings

| Symbol              | Parameter                                            | Min.                              | Max.                              | Unit |

|---------------------|------------------------------------------------------|-----------------------------------|-----------------------------------|------|

| VDDIO               | I/O supply voltage                                   | -0.3                              | 5.0                               | V    |

| VBAT                | Battery supply voltage                               | -0.3                              | 5.0                               |      |

| V <sub>IN</sub>     | Digital input voltage                                | -0.3                              | VDDIO                             |      |

| V <sub>AIN</sub>    | Analog input voltage                                 | -0.3                              | 1.5                               |      |

| V <sub>ESDHBM</sub> | Electrostatic discharge<br>Human Body Model<br>(HBM) | -1000, -2000 (see<br>notes below) | +1000, +2000 (see<br>notes below) |      |

| T <sub>A</sub>      | Storage temperature                                  | -65                               | 150                               | °C   |

| -                   | Junction temperature                                 | -                                 | 125                               |      |

| -                   | RF input power                                       | -                                 | 23                                | dBm  |

- 1.  $V_{IN}$  corresponds to all the digital pins.

- 2. For  $V_{ESDHBM}$ , each pin is classified as Class 1, or Class 2, or both:

- 2.1. The Class 1 pins include all the pins (both analog and digital).

- 2.2. The Class 2 pins include all digital pins only.

- 2.3.  $V_{ESDHBM}$  is ±1 kV for Class 1 pins.  $V_{ESDHBM}$  is ± 2 kV for Class 2 pins.

▲ CAUTION Caution: Stresses beyond those listed under "Absolute Maximum Ratings" cause permanent damage to the device. This is a stress rating only. The functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods affects the device reliability.

### 4.2 Recommended Operating Conditions

The following table provides the recommended operating conditions for the ATWINC3400-MR210CA module.

#### **Electrical Characteristics**

| Symbol | Parameter                                | Min. | Тур. | Max. | Units |

|--------|------------------------------------------|------|------|------|-------|

| VDDIO  | I/O supply voltage <sup>(1)</sup>        | 2.7  | 3.3  | 3.6  | V     |

| VBAT   | Battery supply voltage <sup>(2)(3)</sup> | 3.0  | 3.6  | 4.2  | V     |

| -      | Operating temperature                    | -40  | -    | 85   | °C    |

#### Table 4-2. ATWINC3400-MR210CA Module Recommended Operating Conditions

#### Note:

- 1. I/O supply voltage is applied to the VDDIO pin.

- 2. Battery supply voltage is applied to the VBAT pin.

- 3. The ATWINC3400-MR210CA module is functional across this range of voltages; however, optimal RF performance is guaranteed for VBAT in the range  $\geq$  3.0V VBAT  $\leq$  4.2V.

#### 4.3 DC Characteristics

The following table provides the DC characteristics for the ATWINC3400-MR210CA module digital pads.

| Symbol          | Parameter                            | Min        | Тур | Мах        | Unit |

|-----------------|--------------------------------------|------------|-----|------------|------|

| V <sub>IL</sub> | Input Low<br>Voltage                 | -0.30      | -   | 0.60       | V    |

| V <sub>IH</sub> | Input High<br>Voltage                | VDDIO-0.60 | -   | VDDIO+0.30 |      |

| V <sub>OL</sub> | Output Low<br>Voltage                | -          | -   | 0.45       |      |

| V <sub>OH</sub> | Output High<br>Voltage               | VDDIO-0.50 | -   | -          |      |

| -               | Output Load<br>Capacitance           | -          | -   | 20         | pF   |

| -               | Digital Input<br>Load<br>Capacitance | -          | -   | 6          |      |

#### Table 4-3. DC Electrical Characteristics

#### 4.4 IEEE 802.11 b/g/n Radio Performance

#### 4.4.1 Receiver Performance

The receiver performance is tested under following conditions:

- VBAT = 3.3V

- VDDIO = 3.3V

- Temp = 25°C

- Measured after RF matching network

The following table provides the receiver performance characteristics for the ATWINC3400-MR210CA module.

**Electrical Characteristics**

| Parameter                | Description                          | Min.  | Тур.  | Max.  | Unit |

|--------------------------|--------------------------------------|-------|-------|-------|------|

| Frequency                | -                                    | 2,412 | -     | 2,472 | MHz  |

| Sensitivity 802.11b      | 1 Mbps DSSS                          | -     | -95.0 | -     | dBm  |

|                          | 2 Mbps DSSS                          | -     | -94.0 | -     |      |

|                          | 5.5 Mbps DSSS                        | -     | -90.0 | -     |      |

|                          | 11 Mbps DSSS                         | -     | -86.0 | -     |      |

| Sensitivity 802.11g      | 6 Mbps OFDM                          | -     | -90.0 | -     | dBm  |

|                          | 9 Mbps OFDM                          | -     | -89.0 | -     |      |

|                          | 12 Mbps OFDM                         | -     | -87.0 | -     |      |

|                          | 18 Mbps OFDM                         | -     | -85.0 | -     |      |

|                          | 24 Mbps OFDM                         | -     | -82.0 | -     |      |

|                          | 36 Mbps OFDM                         | -     | -79.0 | -     |      |

|                          | 48 Mbps OFDM                         | -     | -75.0 | -     |      |

|                          | 54 Mbps OFDM                         | -     | -73.0 | -     |      |

| Sensitivity 802.11n      | MCS 0                                | -     | -89.0 | -     | dBm  |

| (BW=20 MHz,<br>800ns GI) | MCS 1                                | -     | -87.0 | -     |      |

| ,                        | MCS 2                                | -     | -84.0 | -     |      |

|                          | MCS 3                                | -     | -82.0 | -     |      |

|                          | MCS 4                                | -     | -78.0 | -     |      |

|                          | MCS 5                                | -     | -75.0 | -     |      |

|                          | MCS 6                                | -     | -73.0 | -     |      |

|                          | MCS 7                                | -     | -71.0 | -     |      |

| Maximum receive          | 1-11 Mbps DSSS                       | -     | 0     | -     | dBm  |

| signal level             | 6-54 Mbps OFDM                       | -     | 0     | -     |      |

|                          | MCS 0 - 7 (800ns GI)                 | -     | 0     | -     |      |

| Adjacent channel         | 1 Mbps DSSS (30 MHz offset)          | -     | 50    | -     | dB   |

| rejection                | 11 Mbps DSSS (25 MHz offset)         | -     | 43    | -     |      |

|                          | 6 Mbps OFDM (25 MHz offset)          | -     | 40    | -     |      |

|                          | 54 Mbps OFDM (25 MHz offset)         | -     | 25    | -     |      |

|                          | MCS 0 – 20 MHz BW (25 MHz<br>offset) | -     | 40    | -     |      |

|                          | MCS 7 – 20 MHz BW (25 MHz offset)    | -     | 20    | -     |      |

#### Table 4-4. IEEE 802.11 Receiver Performance Characteristics

#### 4.4.2 Transmitter Performance

The transmitter performance is tested under following conditions:

- VBAT = 3.3V

- VDDIO = 3.3V

- Temp = 25°C

The following table provides the transmitter performance characteristics for the ATWINC3400-MR210CA module.

| Parameter                                               | Description                      | Minimum | Typical             | Max.  | Unit    |

|---------------------------------------------------------|----------------------------------|---------|---------------------|-------|---------|

| Frequency                                               | -                                | 2,412   | -                   | 2,472 | MHz     |

| Output power                                            | 802.11b 1 Mbps                   | -       | 16.7 <sup>(1)</sup> | -     | dBm     |

|                                                         | 802.11b 11 Mbps                  | -       | 17.5 <sup>(1)</sup> | -     |         |

|                                                         | 802.11g OFDM 6 Mbps              | -       | 18.3 <sup>(1)</sup> | -     |         |

|                                                         | 802.11g OFDM 54 Mbps             | -       | 13.0 <sup>(1)</sup> | -     |         |

|                                                         | 802.11n HT20 MCS 0 (800ns<br>GI) | -       | 17.5 <sup>(1)</sup> | -     |         |

|                                                         | 802.11n HT20 MCS 7 (800ns<br>GI) | -       | 12.5 <sup>(1)</sup> | -     |         |

| Tx power accuracy                                       | -                                | -       | ±1.5 <sup>(2)</sup> | -     | dB      |

| Carrier suppression                                     | -                                | -       | 30.0                | -     | dBc     |

| Harmonic output<br>power (Radiated,<br>Regulatory mode) | 2 <sup>nd</sup>                  | -       | -                   | -41   | dBm/MHz |

|                                                         | 3rd                              | -       | -                   | -41   |         |

#### Table 4-5. IEEE 802.11 Transmitter Performance Characteristics

#### Note:

- 1. Measured at IEEE 802.11 specification compliant EVM/Spectral mask.

- 2. Measured after RF matching network.

- 3. Operating temperature range is -40°C to +85°C. RF performance guaranteed at room temperature of 25°C with a 2-3dB change at boundary conditions.

- 4. With respect to Tx power, different (higher/lower) RF output power settings may be used for specific antennas and/or enclosures, in which case recertification may be required.

- 5. The availability of some specific channels and/or operational frequency bands are country dependent and should be programmed at the host product factory to match the intended destination. Regulatory bodies prohibit exposing the settings to the end user. This requirement needs to be taken care of via host implementation.

#### 4.5 Bluetooth Radio Performance

#### 4.5.1 Receiver Performance

The receiver performance is tested under following conditions:

- VBAT = 3.3V

- VDDIO = 3.3V

- Temp: 25°C

- Measured after RF matching network

The following table provides the Bluetooth receiver performance characteristics for the ATWINC3400-MR210CA module.

#### Table 4-6. Bluetooth Receiver Performance Characteristics

| Parameter                    | Description                          | Min.  | Тур.  | Max.  | Unit |

|------------------------------|--------------------------------------|-------|-------|-------|------|

| Frequency                    | -                                    | 2,402 | -     | 2,480 | MHz  |

| Sensitivity (ideal Tx)       | Bluetooth Low Energy (GFSK)          | -     | -92.5 | -     | dBm  |

| Maximum receive signal level | Bluetooth Low Energy (GFSK)          | -     | -2    | -     |      |

| Interference performance     | Co-channel                           | -     | 9     |       | dB   |

| (Bluetooth Low Energy)       | adjacent + 1 MHz                     | -     | -4    | -     |      |

|                              | adjacent - 1 MHz                     | -     | -2    | -     |      |

|                              | adjacent + 2 MHz(image<br>frequency) | -     | -24   | -     |      |

|                              | adjacent - 2 MHz                     | -     | -25   | -     |      |

|                              | adjacent + 3 MHz (adjacent to image) | -     | -27   | -     |      |

|                              | adjacent - 3 MHz                     | -     | -27   | -     |      |

|                              | adjacent + 4 MHz                     | -     | -28   | -     |      |

|                              | adjacent - 4 MHz                     | -     | -27   | -     |      |

|                              | adjacent +5 MHz                      | -     | -27   | -     |      |

|                              | adjacent - 5 MHz                     | -     | -27   | -     |      |

#### 4.5.2 Transmitter Performance

The transmitter performance is tested under following conditions:

- VBAT = 3.3V

- VDDIO = 3.3V

- Temp: 25°C

- Measured after RF matching network.

The following table provides the Bluetooth transmitter performance characteristics for the ATWINC3400-MR210CA module.

**Electrical Characteristics**

| Parameter                                              | Description                         | Min.  | Тур. | Max.  | Unit |  |

|--------------------------------------------------------|-------------------------------------|-------|------|-------|------|--|

| Frequency                                              | -                                   | 2,402 | -    | 2,480 | MHz  |  |

| Output power                                           | Bluetooth Low Energy (GFSK)         | -     | 3.3  | 3.8   | dBm  |  |

| In-band spurious<br>emission (Bluetooth Low<br>Energy) | N+2 (Image frequency)               | -     | -33  | -     |      |  |

|                                                        | N + 3 (Adjacent to image frequency) | -     | -32  | -     |      |  |

|                                                        | N-2                                 | -     | -48  | -     |      |  |

|                                                        | N-3                                 | -     | -47  | -     |      |  |

#### Table 4-7. Bluetooth Transmitter Performance Characteristics

### 4.6 Timing Characteristics

#### 4.6.1 I<sup>2</sup>C Slave Timing

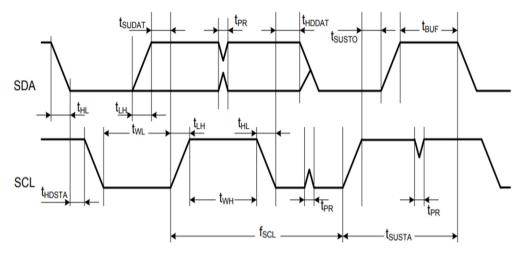

The I<sup>2</sup>C Slave timing diagram for the ATWINC3400-MR210CA module is shown in the following figure.

### Figure 4-1. I<sup>2</sup>C Slave Timing Diagram

The following table provides the I<sup>2</sup>C Slave timing parameters for the ATWINC3400-MR210CA module.

#### Table 4-8. I<sup>2</sup>C Slave Timing Parameters

| Parameter            | Symbol           | Min. | Max. | Units | Remarks                                 |

|----------------------|------------------|------|------|-------|-----------------------------------------|

| SCL Clock Frequency  | f <sub>SCL</sub> | 0    | 400  | kHz   | -                                       |

| SCL Low Pulse Width  | t <sub>WL</sub>  | 1.3  | -    |       | -                                       |

| SCL High Pulse Width | t <sub>WH</sub>  | 0.6  | -    | μs    | -                                       |

| SCL, SDA Fall Time   | t <sub>HL</sub>  | -    | 300  |       | -                                       |

| SCL, SDA Rise Time   | t <sub>LH</sub>  | -    | 300  | ns    | This is dictated by external components |

### **Electrical Characteristics**

| Parameter                               | Symbol             | Min. | Max. | Units | Remarks                      |

|-----------------------------------------|--------------------|------|------|-------|------------------------------|

| START Setup Time                        | t <sub>SUSTA</sub> | 0.6  | -    |       | -                            |

| START Hold Time                         | t <sub>HDSTA</sub> | 0.6  | -    | μs    | -                            |

| SDA Setup Time                          | t <sub>SUDAT</sub> | 100  | -    | ns    | -                            |

| SDA Hold Time                           | t <sub>HDDAT</sub> | 0    | -    | ns    | Slave and Master Default     |

|                                         |                    | 40   | -    | μs    | Master Programming<br>Option |

| STOP Setup Time                         | t <sub>susto</sub> | 0.6  | -    |       | -                            |

| Bus Free Time Between<br>STOP and START | t <sub>BUF</sub>   | 1.3  | -    | μs    | -                            |

| Glitch Pulse Reject                     | t <sub>PR</sub>    | 0    | 50   | ns    | -                            |

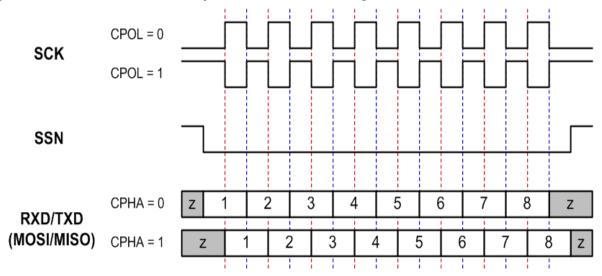

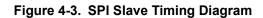

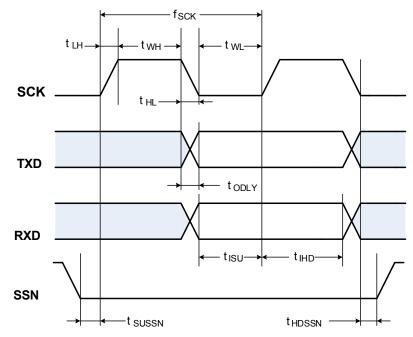

#### 4.6.2 SPI Slave Timing

The SPI Slave timing for the ATWINC3400-MR210CA module is provided in the following figures. **Figure 4-2. SPI Slave Clock Polarity and Clock Phase Timing**

### **Electrical Characteristics**

The following table provides the SPI Slave timing parameters for the ATWINC3400-MR210CA module. **Table 4-9. SPI Slave Timing Parameters** <sup>(1)</sup>

| Parameter                       | Symbol            | Min. | Max.                                | Unit |

|---------------------------------|-------------------|------|-------------------------------------|------|

| Clock Input Frequency (2)       | f <sub>SCK</sub>  | -    | 48                                  | MHz  |

| Clock Low Pulse Width           | t <sub>VVL</sub>  | 6    | -                                   | ns   |

| Clock High Pulse Width          | t <sub>WH</sub>   | 4    | -                                   |      |

| Clock Rise Time                 | t <sub>LH</sub>   | 0    | 7                                   |      |

| Clock Fall Time                 | t <sub>HL</sub>   | 0    | 7                                   |      |

| TXD Output Delay <sup>(3)</sup> | t <sub>ODLY</sub> | 3    | 9 from SCK fall<br>11 from SCK rise |      |

| RXD Input Setup Time            | t <sub>ISU</sub>  | 3    | -                                   |      |

| RXD Input Hold Time             | t <sub>IHD</sub>  | 5    | -                                   |      |

**Electrical Characteristics**

| Parameter            | Symbol             | Min. | Max. | Unit |

|----------------------|--------------------|------|------|------|

| SSN Input Setup Time | t <sub>SUSSN</sub> | 5    | -    |      |

| SSN Input Hold Time  | t <sub>HDSSN</sub> | 5    | -    |      |

#### Note:

- 1. Timing is applicable to all SPI modes.

- 2. Maximum clock frequency specified is limited by the SPI Slave interface internal design; actual maximum clock frequency can be lower and depends on the specific PCB layout.

- 3. Timing based on 15 pF output loading.

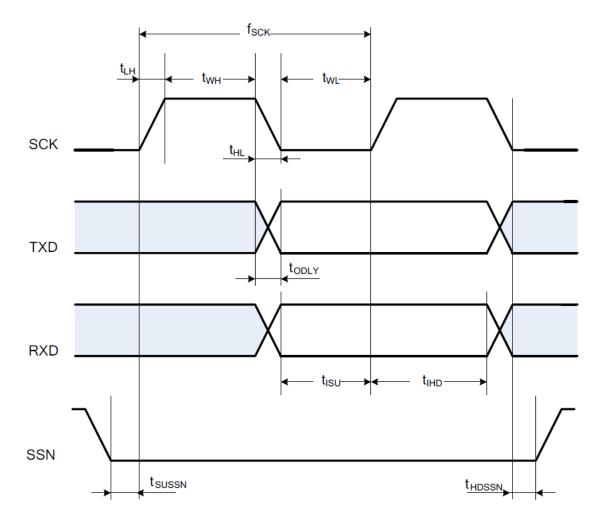

#### 4.6.3 SPI Master Timing

The SPI Master timing for the ATWINC3400-MR210CA module is shown in the following figure. **Figure 4-4. SPI Master Timing Diagram**

The following table provides the SPI Master timing parameters for the ATWINC3400-MR210CA module .

Table 4-10. SPI Master Timing Parameters <sup>(1)</sup>

| Parameter                             | Symbol            | Min. | Max. | Unit |

|---------------------------------------|-------------------|------|------|------|

| Clock Output Frequency <sup>(2)</sup> | f <sub>SCK</sub>  | -    | 20   | MHz  |

| Clock Low Pulse Width                 | t <sub>WL</sub>   | 19   | -    | ns   |

| Clock High Pulse Width                | t <sub>WH</sub>   | 21   | -    |      |

| Clock Rise Time <sup>(3)</sup>        | t <sub>LH</sub>   | -    | 11   |      |

| Clock Fall Time (3)                   | t <sub>HL</sub>   | -    | 10   |      |

| RXD Input Setup Time                  | t <sub>ISU</sub>  | 24   | -    |      |

| RXD Input Hold Time                   | t <sub>IHD</sub>  | 0    | -    |      |

| SSN/TXD Output Delay <sup>(3)</sup>   | t <sub>ODLY</sub> | -5   | 3    |      |

### **Electrical Characteristics**

#### Note:

- 1. Timing is applicable to all SPI modes.

- 2. Maximum clock frequency specified is limited by the SPI Master interface internal design; actual maximum clock frequency can be lower and depends on the specific PCB layout.

- 3. Timing based on 15 pF output loading.

### 5. Power Management

#### 5.1 Device States

The ATWINC3400-MR210CA module has multiple device states, based on the state of the IEEE 802.11 and Bluetooth subsystems. It is possible for both subsystems to be active at the same time. To simplify the device power consumption breakdown, the following basic states are defined. One subsystem can be active at a time:

- WiFi\_ON\_Transmit Device actively transmits IEEE 802.11 signal

- WiFi\_ON\_Receive Device actively receives IEEE 802.11 signal

- BT\_ON\_Transmit Device actively transmits Bluetooth signal

- BT\_ON\_Receive Device actively receives Bluetooth signal

- Doze Device is powered on but it does not actively transmit or receive data

- Power\_Down Device core supply is powered off

#### 5.2 Controlling Device States

The following table shows different device states and its power consumption. The device states can be switched using the following:

- CHIP\_EN Module pin (pin 19) enables or disables the DC/DC converter

- VDDIO I/O supply voltage from external supply

In the ON states, VDDIO is ON and CHIP\_EN is high (at VDDIO voltage level). To change from the ON states to Power\_Down state, connect the RESETN and CHIP\_EN pin to logic low (GND) by following the power-down sequence mentioned in Figure 5-1. When VDDIO is OFF and CHIP\_EN is low, the chip is powered off with no leakage.

| Device State     | Code Rate       | Output Power | Current Cons      | sumption <sup>(1)</sup> |

|------------------|-----------------|--------------|-------------------|-------------------------|

| Device State     |                 | (dBm)        | I <sub>VBAT</sub> | I <sub>VDDIO</sub>      |

| ON_WiFi_Transmit | 802.11b 1 Mbps  | 16.7         | 271 mA            | 24 mA                   |

|                  | 802.11b 11 Mbps | 17.5         | 265 mA            | 24 mA                   |

|                  | 802.11g 6 Mbps  | 18.3         | 275 mA            | 24 mA                   |

|                  | 802.11g 54 Mbps | 13.0         | 235 mA            | 24 mA                   |

|                  | 802.11n MCS 0   | 17.5         | 272 mA            | 24 mA                   |

|                  | 802.11n MCS 7   | 12.5         | 232 mA            | 24 mA                   |

| ON_WiFi_Receive  | 802.11b 1 Mbps  | N/A          | 63.9 mA           | 23.7 mA                 |

|                  | 802.11b 11 Mbps | N/A          | 63.9 mA           | 23.7 mA                 |

|                  | 802.11g 6 Mbps  | N/A          | 63.9 mA           | 23.7 mA                 |

|                  | 802.11g 54 Mbps | N/A          | 63.9 mA           | 23.7 mA                 |

Table 5-1. ATWINC3400-MR210CA Device States Current Consumption

#### **Power Management**

| Device State                             | Code Rate      | Output Power | Current Consumption <sup>(1)</sup> |                    |  |

|------------------------------------------|----------------|--------------|------------------------------------|--------------------|--|

| Device State                             |                | (dBm)        | I <sub>VBAT</sub>                  | I <sub>VDDIO</sub> |  |

|                                          | 802.11n MCS 0  | N/A          | 63.9 mA                            | 23.7 mA            |  |

|                                          | 802.11n MCS 7  | N/A          | 63.9 mA                            | 23.7 mA            |  |

| ON_BT_Transmit                           | BLE 4.0 1 Mbps | 3.3          | 79.37 mA 23.68 m                   |                    |  |

| ON_BT_Receive                            | BLE 4.0 1 Mbps | N/A          | 51.36 mA                           | 23.68 mA           |  |

| Doze (Bluetooth Low<br>Energy Idle)      | N/A            | N/A          | 53 mA <sup>(2)</sup>               |                    |  |

| Doze (Bluetooth Low<br>Energy Low Power) | N/A            | N/A          | 1 mA <sup>(2)</sup>                |                    |  |

| Power_Down                               | N/A            | N/A          | 10.5 uA <sup>(2)</sup>             |                    |  |

#### Note:

- 1. Conditions: VBAT = 3.3V, VDDIO = 3.3V, at  $25^{\circ}C$ .

- 2. Current consumption mentioned for these states is the sum of current consumed in VDDIO and VBAT voltage rails.

When power is not supplied to the device (DC/DC converter output and VDDIO are OFF, at ground potential), voltage cannot be applied to the ATWINC3400-MR210CA module pins because each pin contains an ESD diode from the pin to supply. This diode turns on when voltage higher than one diode-drop is supplied to the pin.

If voltage must be applied to the signal pads when the chip is in a low-power state, the VDDIO supply must be ON, so the Power\_Down state must be used. Similarly, to prevent the pin-to-ground diode from turning ON, do not apply voltage that is more than one diode-drop below the ground to any pin.

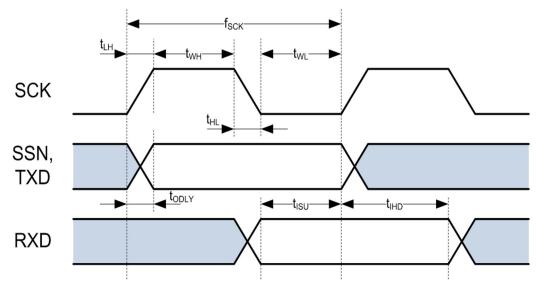

#### 5.3 Power-Up/Down Sequence

The following figure illustrates the power-up/down sequence for the ATWINC3400-MR210CA module.

Figure 5-1. Power-Up/Down Sequence

The following table provides power-up/down sequence timing parameters.

#### **Power Management**

| Paramet<br>er   | Min. | Max. | Unit<br>s | Description                    | Notes                                                                                                                                          |

|-----------------|------|------|-----------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>A</sub>  | 0    | -    | ms        | VBAT rise to<br>VDDIO rise     | VBAT and VDDIO can rise simultaneously or connected together. VDDIO must not rise before VBAT.                                                 |

| t <sub>B</sub>  | 0    | -    | ms        | VDDIO rise to<br>CHIP_EN rise  | CHIP_EN must not rise before VDDIO. CHIP_EN must be driven high or low and must not be left floating.                                          |

| t <sub>C</sub>  | 5    | -    | ms        | CHIP_EN rise to<br>RESETN rise | This delay is required to stabilize the XO clock<br>before RESETN removal. RESETN must be driven<br>high or low and must not be left floating. |

| t <sub>A'</sub> | 0    | -    | ms        | VDDIO fall to<br>VBAT fall     | VBAT and VDDIO fall simultaneously or connected together. VBAT must not fall before VDDIO.                                                     |

| t <sub>B'</sub> | 0    | -    | ms        | CHIP_EN fall to VDDIO fall     | VDDIO must not fall before CHIP_EN. CHIP_EN and RESETN must fall simultaneously.                                                               |

| t <sub>C'</sub> | 0    | -    | ms        | RESETN fall to<br>VDDIO fall   | VDDIO must not fall before RESETN. RESETN and CHIP_EN fall simultaneously.                                                                     |

| Table 5-2. Power-Up/Down Sequence Timing | Table 5-2. | Power-Up/D | own Sequence | • Timing |

|------------------------------------------|------------|------------|--------------|----------|

|------------------------------------------|------------|------------|--------------|----------|

### 5.4 Digital I/O Pin Behavior During Power-Up Sequences

The following table represents the digital I/O pin states corresponding to the device power modes.

| Device State                                                                             | VDDIO | CHIP_E<br>N | RESET<br>N | Output Driver                                                        | Input<br>Driver                             | Pull Up/Down<br>Resistor (96<br>kOhm)                                |

|------------------------------------------------------------------------------------------|-------|-------------|------------|----------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------|

| Power_Down: core supply OFF                                                              | High  | Low         | Low        | Disabled (Hi-Z)                                                      | Disabled                                    | Disabled                                                             |

| Power-On Reset: core supply and hard reset ON                                            | High  | High        | Low        | Disabled (Hi-Z)                                                      | Disabled                                    | Enabled                                                              |

| Power-On Default: core<br>supply ON, device out of<br>reset and not programmed           | High  | High        | High       | Disabled (Hi-Z)                                                      | Enabled                                     | Enabled                                                              |

| On_Doze/ On_Transmit/<br>On_Receive: core supply<br>ON, device programmed by<br>firmware | High  | High        | High       | Programmed<br>by firmware for<br>each pin:<br>enabled or<br>disabled | Opposite<br>of<br>Output<br>Driver<br>state | Programmed by<br>firmware for<br>each pin:<br>enabled or<br>disabled |

## 6. Clocking

### 6.1 Low-Power Clock

The ATWINC3400-MR210CA module requires an external 32.768 kHz clock to be supplied at the module pin 20. This clock is used during the sleep operation. The frequency accuracy of this external clock must be within ±200 ppm.

## 7. CPU and Memory Subsystem

#### 7.1 Processor

The ATWINC3400-MR210CA module has two Cortus APS3 32-bit processors, one is used for Wi-Fi and the other is used for Bluetooth. In IEEE 802.11 mode, the processor performs many of the MAC functions, including but not limited to: association, authentication, power management, security key management, and MSDU aggregation/de-aggregation. In addition, the processor provides flexibility for various modes of operation, such as Station (STA) and Access Point (AP) modes. In Bluetooth mode, the processor handles multiple tasks of the Bluetooth protocol stack.

### 7.2 Memory Subsystem

The APS3 core uses a 256 KB instruction/boot ROM (160 KB for IEEE 802.11 and 96 KB for Bluetooth) along with a 420 KB instruction RAM (128 KB for IEEE 802.11 and 292 KB for Bluetooth), and a 128 KB data RAM (64 KB for IEEE 802.11 and 64 KB for Bluetooth). In addition, the device uses a 160 KB shared/exchange RAM (128 KB for IEEE 802.11 and 32 KB for Bluetooth), accessible by the processor and MAC, which allows the processor to perform various data management tasks on the Tx and Rx data packets.

### 7.3 Nonvolatile Memory

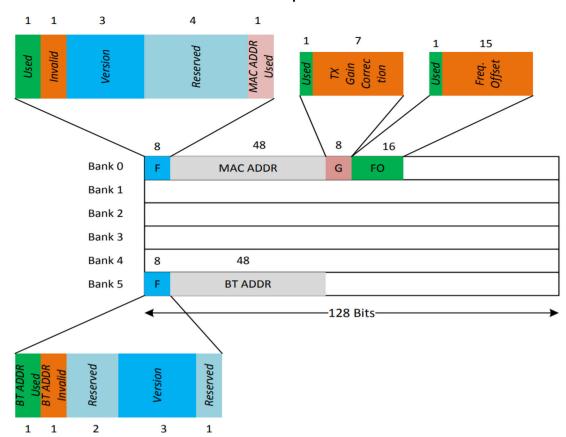

The ATWINC3400-MR210CA module has 768 bits of nonvolatile eFuse memory that can be read by the CPU after device reset. This nonvolatile One-Time-Programmable (OTP) memory can be used to store customer-specific parameters, such as the 802.11 MAC address and Bluetooth address; and various calibration information such as Tx power, crystal frequency offset, and other software-specific configuration parameters. The eFuse is partitioned into six 128-bit banks. The bit map of the first and last banks is shown in the following figure. The purpose of the first 80 bits in bank 0 and the first 56 bits in bank 5 is fixed, and the remaining bits are general-purpose software dependent bits, reserved for future use. Currently, the Bluetooth address is derived from the Wi-Fi MAC address (BT\_ADDR=MAC\_ADDR +1). This eliminates the need to program the first 56 bits in bank 5. Since each bank and each bit can be programmed independently, this allows for several updates of the device parameters following the initial programming. For example, if the MAC address has to be changed, Bank 1 has to be programmed with the new MAC address along with the values of Tx gain correction and frequency offset if they are used and programmed in the Bank 0. The contents of Bank 0 have to be invalidated in this case by programming the Invalid bit in the Bank 0. This will allow the firmware to use the MAC address from Bank 1.

By default, ATWINC3400-MR210CA modules are programmed with the MAC address and the frequency offset bits of Bank 0.

**CPU and Memory Subsystem**

#### Figure 7-1. ATWINC3400-MR210CA eFuse Bit Map

### 8. WLAN Subsystem

The WLAN subsystem is composed of the Media Access Controller (MAC), Physical Layer (PHY), and the radio.

### 8.1 MAC

The ATWINC3400-MR210CA module is designed to operate at low power, while providing high data throughput. The IEEE 802.11 MAC functions are implemented with a combination of dedicated datapath engines, hardwired control logic, and a low power, high-efficiency microprocessor. The combination of dedicated logic with a programmable processor provides optimal power efficiency and real time response while providing the flexibility to accommodate evolving standards and future feature enhancements.

The dedicated datapath engines are used to implement datapath functions with heavy computational requirements. For example, a Frame Check Sequence (FCS) engine checks the Cyclic Redundancy Check (CRC) of the transmitting and receiving packets, and a cipher engine performs all the required encryption and decryption operations for the WEP, WPA-TKIP, and WPA2 CCMP-AES security requirements.

Control functions, which have real time requirements, are implemented using hardwired control logic modules. These logic modules offer real time response while maintaining configurability through the processor. Examples of hardwired control logic modules are the channel access control module (implements EDCA/HCCA, Beacon Tx control, interframe spacing, and so on), protocol timer module (responsible for the Network Access vector, back-off timing, timing synchronization function, and slot management), MAC Protocol Data Unit (MPDU) handling module, aggregation/deaggregation module, block ACK controller (implements the protocol requirements for burst block communication), and Tx/Rx control Finite State Machine (FSM) (coordinates data movement between PHY and MAC interface, cipher engine, and the Direct Memory Access (DMA) interface to the Tx/Rx FIFOs).

The following are the characteristics of MAC functions implemented solely in software on the microprocessor:

- Functions with high memory requirements or complex data structures. Examples include association table management and power save queuing.

- Functions with low computational load or without critical real time requirements. Examples include authentication and association.

- Functions that require flexibility and upgradeability. Examples include beacon frame processing and QoS scheduling.

#### Features

The ATWINC3400-MR210CA MAC supports the following functions:

- IEEE 802.11b/g/n

- IEEE 802.11e WMM QoS EDCA/HCCA/PCF multiple access categories traffic scheduling

- Advanced IEEE 802.11n features:

- Transmission and reception of aggregated MPDUs (A-MPDU)

- Transmission and reception of aggregated MSDUs (A-MSDU)

- Immediate block acknowledgment

- Reduced Interframe Spacing (RIFS)

- IEEE 802.11i and WFA security with key management:

- WEP 64/128

- WPA-TKIP

- 128-bit WPA2 CCMP (AES)

- Advanced power management:

- Standard IEEE 802.11 power save mode

- RTS-CTS and CTS-self support

- Either STA or AP mode in the infrastructure basic service set mode

#### 8.2 PHY

The ATWINC3400-MR210CA module WLAN PHY is designed to achieve reliable and power-efficient physical layer communication specified by IEEE 802.11 b/g/n in single stream mode with 20 MHz bandwidth. The advanced algorithms are used to achieve maximum throughput in a real world communication environment with impairments and interference. The PHY implements all the required functions such as Fast Fourier Transform (FFT), filtering, Forward Error Correction (FEC) that is a Viterbi decoder, frequency, timing acquisition and tracking, channel estimation and equalization, carrier sensing, clear channel assessment and automatic gain control.

#### Features

The IEEE 802.11 PHY supports the following functions:

- Single antenna 1x1 stream in 20 MHz channels

- Supports IEEE 802.11b DSSS-CCK modulation: 1, 2, 5.5, and 11 Mbps

- Supports IEEE 802.11g OFDM modulation: 6, 9, 12,18, 24, 36, 48, and 54 Mbps

- Supports IEEE 802.11n HT modulations MCS0-7, 20 MHz, 800 and 400ns guard interval: 6.5, 7.2, 13.0, 14.4, 19.5, 21.7, 26.0, 28.9, 39.0, 43.3, 52.0, 57.8, 58.5, 65.0, and 72.2 Mbps

- IEEE 802.11n mixed mode operation

- Per packet Tx power control

- Advanced channel estimation/equalization, automatic gain control, CCA, carrier/symbol recovery and frame detection

#### 8.3 Radio

This section presents information describing the properties and characteristics of the ATWINC3400-MR210CA and Wi-Fi radio transmit and receive performance capabilities of the device.

The performance measurements are taken at the RF pin assuming 50 $\Omega$  impedance; the RF performance is guaranteed for room temperature of 25°C with a derating of 2-3 dB at boundary conditions.

Measurements were taken under typical conditions: VBATT=3.3V; VDDIO=3.3V; temperature: +25°C

#### Table 8-1. Features and Properties

| Feature        | Description                        |

|----------------|------------------------------------|

| Part Number    | ATWINC3400-MR210CA                 |

| WLAN Standard  | IEEE 802.11 b/g/n, Wi-Fi compliant |

| Host Interface | SPI                                |

## WLAN Subsystem

| Feature                                  | Description                                                              |

|------------------------------------------|--------------------------------------------------------------------------|

| Dimension                                | 22.4 x 14.7 x 2.0 mm                                                     |

| Frequency Range                          | 2.412GHz ~ 2.472GHz (2.4GHz ISM Band)                                    |

| Number of Channels                       | 11 for North America, and 13 for Europe and Japan                        |

| Modulation                               | 802.11b: DQPSK, DBPSK, CCK<br>802.11g/n: OFDM /64-QAM,16-QAM, QPSK, BPSK |

| Data Rate                                | 802.11b: 1, 2, 5.5, 11Mbps                                               |

|                                          | 802.11g: 6, 9, 12, 18, 24, 36, 48, 54Mbps                                |

| Data Rate<br>(20 MHz, normal GI, 800 ns) | 802.11n: 6.5, 13, 19.5, 26, 39, 52, 58.5, 65Mbps                         |

| Data Rate<br>(20 MHz, short GI, 400 ns)  | 802.11n: 7.2, 14.4, 21.7, 28.9, 43.3, 57.8,<br>65,72.2Mbps               |

| Operating temperature                    | -40 to +85°C                                                             |

## 9. Bluetooth Low Energy 4.0

The Bluetooth subsystem implements all the mission critical real-time functions. It encodes/decodes HCI packets, constructs baseband data packages; and manages and monitors the connection status, slot usage, data flow, routing, segmentation, and buffer control. The Bluetooth subsystem supports Bluetooth Low Energy modes of operation.

Supports the following advanced low energy applications:

- Smart energy

- Consumer wellness

- Home automation

- Security

- Proximity detection

- Entertainment

- Sports and Fitness

- Automotive

#### **Coexistence Mechanism**

The ATWINC3400 supports simultaneous usage of both Bluetooth Low Energy and Wi-Fi via a coexistence mechanism that allows the protocols to share the same radio. The radio defaults to Wi-Fi usage until a Bluetooth Low Energy event occurs (such as connection or advertising), in which case the radio is gracefully switched over for Bluetooth Low Energy use. For the duration of the Bluetooth Low Energy event, the radio is switched back and forth between Wi-Fi and Bluetooth Low Energy as demanded by the Bluetooth Low Energy activity, before returning to Wi-Fi until the next Bluetooth Low Energy event.

### 10. External Interfaces

### 10.1 Interfacing with the Host Microcontroller

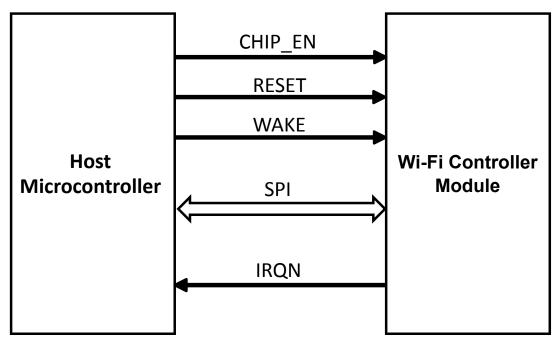

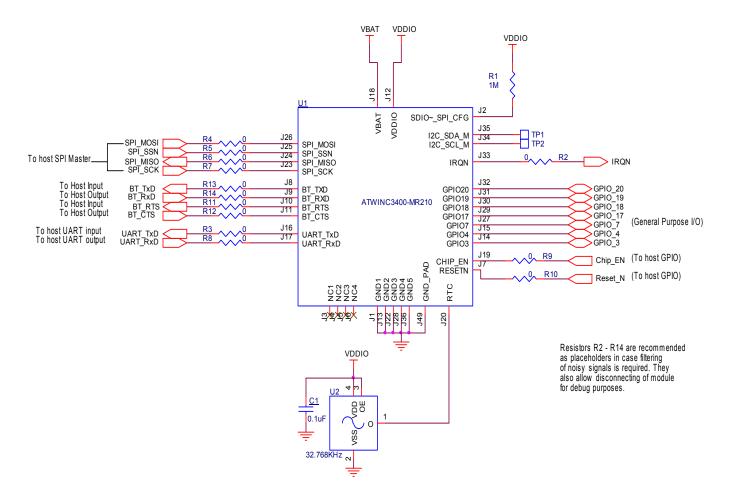

This section describes interfacing the ATWINC3400-MR210CA module with the host microcontroller. The interface is comprised of a slave SPI and additional control signals, as shown in the following figure. For more information on SPI interface specification and timing, refer to the SPI Interface. Additional control signals are connected to the GPIO/IRQ interface of the microcontroller.

#### Figure 10-1. Interfacing with Host Microcontroller

Table 10-1. Host Microcontroller Interface Pins

| Pin Number | Function |

|------------|----------|

| 4          | RESET_N  |

| 11         | WAKE     |

| 13         | IRQ_N    |

| 22         | CHIP_EN  |

| 16         | SPI_SSN  |

| 15         | SPI_MOSI |

| 17         | SPI_MISO |

| 18         | SPI_SCK  |

#### **Related Links**

SPI Interface

#### 10.2 SPI Interface

#### 10.2.1 Overview

The ATWINC3400-MR210CA has a Serial Peripheral Interface (SPI) that operates as an SPI slave. The SPI interface can be used for control and for serial I/O of 802.11 data. The SPI pins are mapped as shown in the following table. The SPI is a full-duplex slave-synchronous serial interface that is available immediately following reset when pin 10 (SPI\_CFG) is tied to VDDIO.

| Pin # | SPI function                    |

|-------|---------------------------------|

| 10    | CFG: Must be tied to VDDIO      |

| 16    | SSN: Active-Low Slave Select    |

| 15    | MOSI(RXD): Serial Data Receive  |

| 18    | SCK: Serial Clock               |

| 17    | MISO(TXD): Serial Data Transmit |

Table 10-2. SPI Interface Pin Mapping

When the SPI is not selected, that is, when SSN is high, the SPI interface will not interfere with data transfers between the serial-master and other serial-slave devices. When the serial slave is not selected, its transmitted data output is buffered, resulting in a high impedance drive onto the MISO line.

The SPI interface responds to a protocol that allows an external host to read or write any register in the chip as well as initiate DMA transfers.

The SPI SSN, MOSI, MISO, and SCK pins of the ATWINC3400-MR210CA have internal programmable pull-up resistors. These resistors should be programmed to be disabled; otherwise, if any of the SPI pins are driven to a low level while the ATWINC3400-MR210CA is in the low power sleep state, the current will flow from the VDDIO supply through the pull-up resistors, increasing the current consumption of the module.

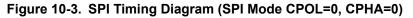

#### 10.2.2 SPI Timing

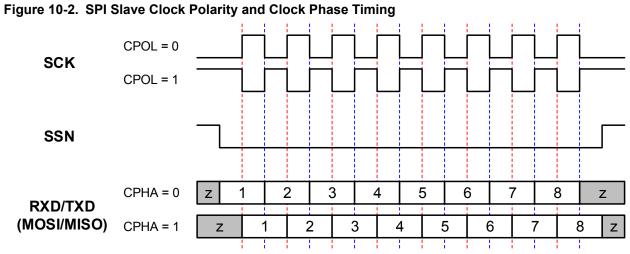

The SPI Slave interface supports four standard modes as determined by the Clock Polarity (CPOL) and Clock Phase (CPHA) settings. These modes are illustrated in the following table and figure.

| Mode | CPOL | СРНА |

|------|------|------|

| 0    | 0    | 0    |

| 1    | 0    | 1    |

| 2    | 1    | 0    |

| 3    | 1    | 1    |

#### Table 10-3. SPI Slave Modes

The red lines in the following figure correspond to Clock Phase = 0 and the blue lines correspond to Clock Phase = 1.

#### **External Interfaces**

The SPI timing is provided in the following figure and table.

| Parameter                          | Symbol           | Min. | Max. | Units |

|------------------------------------|------------------|------|------|-------|

| Clock Input Frequency <sup>2</sup> | f <sub>SCK</sub> | —    | 48   | MHz   |

| Clock Low Pulse Width              | t <sub>WL</sub>  | 4    | —    |       |

| Clock High Pulse Width             | t <sub>WH</sub>  | 5    | —    | 20    |

| Clock Rise Time                    | t <sub>LH</sub>  | 0    | 7    | ns    |

| Clock Fall Time                    | t <sub>HL</sub>  | 0    | 7    |       |

#### **External Interfaces**

| Parameter                     | Symbol             | Min. | Max.                                     | Units |

|-------------------------------|--------------------|------|------------------------------------------|-------|

| TXD Output Delay <sup>3</sup> | t <sub>ODLY</sub>  | 4    | 9 from SCK fall<br>12.5 from SCK<br>rise |       |

| RXD Input Setup Time          | t <sub>ISU</sub>   | 1    | —                                        |       |

| RXD Input Hold Time           | t <sub>IHD</sub>   | 5    | —                                        |       |

| SSN Input Setup Time          | t <sub>SUSSN</sub> | 3    | —                                        |       |

| SSN Input Hold Time           | t <sub>HDSSN</sub> | 5.5  | —                                        |       |

#### Note:

- 1. Timing is applicable to all SPI modes

- 2. Maximum clock frequency specified is limited by the SPI Slave interface internal design, actual maximum clock frequency can be lower and depends on the specific PCB layout

- 3. Timing based on 15pF output loading

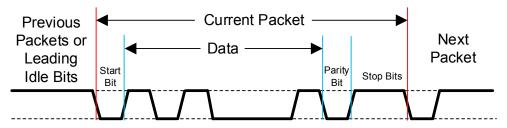

#### 10.3 UART Interface

The ATWINC3400-MR210CA supports the Universal Asynchronous Receiver/Transmitter (UART) interface. This interface should be used for debug purposes only. The two UART pins TXD/RXD are available on pin J16 and pin J17 respectively. The UART is compatible with the RS-232 standard.

The default configuration for accessing the UART interface of ATWINC3400-MR210CA is mentioned below:

- Baud rate: 460800

- Data: 8 bit

- Parity: None

- Stop bit: 1 bit

- Flow control: None

It also has RX and TX FIFOs, which ensure reliable high-speed reception and low software overhead transmission. FIFO size is 4 x 8 for both RX and TX direction. The UART also has status registers showing the number of received characters available in the FIFO and various error conditions, as well the ability to generate interrupts based on these status bits.

An example of the UART receiving or transmitting a single packet is shown in the following figure. This example shows 7-bit data (0x45), odd parity, and two stop bits.