# Application Manual

Real Time Clock Module

RTC-72421 / 72423

### **NOTICE**

- This material is subject to change without notice.

- Any part of this material may not be reproduced or duplicated in any form or any means without the written permission of Seiko Epson.

- The information about applied circuitry, software, usage, etc. written in this material is intended for reference only. Seiko Epson does not assume any liability for the occurrence of infringing on any patent or copyright of a third party. This material does not authorize the licensing for any patent or intellectual copyrights.

- When exporting the products or technology described in this material, you should comply with the

applicable export control laws and regulations and follow the procedures required by such laws and

regulations.

- You are requested not to use the products (and any technical information furnished, if any) for the

development and/or manufacture of weapon of mass destruction or for other military purposes. You

are also requested that you would not make the products available to any third party who may use the

products for such prohibited purposes.

- These products are intended for general use in electronic equipment. When using them in specific

applications that require extremely high reliability, such as the applications stated below, you must

obtain permission from Seiko Epson in advance.

- / Space equipment (artificial satellites, rockets, etc.) / Transportation vehicles and related (automobiles, aircraft, trains, vessels, etc.) / Medical instruments to sustain life / Submarine transmitters / Power stations and related / Fire work equipment and security equipment / traffic control equipment / and others requiring equivalent reliability.

- All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective.

# **CONTENTS**

| ■ Overview                                                                                                                                                                                                                                                                                                   | 1              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| ■ Block diagram                                                                                                                                                                                                                                                                                              | 1              |

| ■ Terminal connections                                                                                                                                                                                                                                                                                       | 2              |

| ■ Terminal functions                                                                                                                                                                                                                                                                                         | 3              |

| Characteristics  1. Absolute maximum ratings 2. Recommended operating conditions. 3. Frequency characteristics and current consumption characteristics 4. Electrical characteristics ( DC characteristics )                                                                                                  | 4<br>4<br>4    |

| Switching characteristics (AC characteristics)  1. When ALE is used  2. When ALE is fixed at VDD.                                                                                                                                                                                                            | 5              |

| <ul> <li>Registers</li> <li>1. Register table</li> <li>2. Notes</li> <li>3. Functions of register bits (overview)</li> <li>4. Setting the fixed-period pulse output mode and fixed-period interrupt mode</li> <li>5. Resetting the fixed-period pulse output mode and fixed-period interrupt mode</li> </ul> | 7<br>7<br>8    |

| ■ Register description  1. Timing registers  2. CD register (control register D)  3. CE register (control register E)  4. CF register (control register F)                                                                                                                                                   | 9<br>10<br>11  |

| ■ Using the RTC-72421/RTC-72423  1. Power-on procedure (initialization).  2. Read/write of S1 to W registers.  3. Write to 30-second ADJ bit.  4. Using the CS1 pin.                                                                                                                                         | 14<br>16<br>16 |

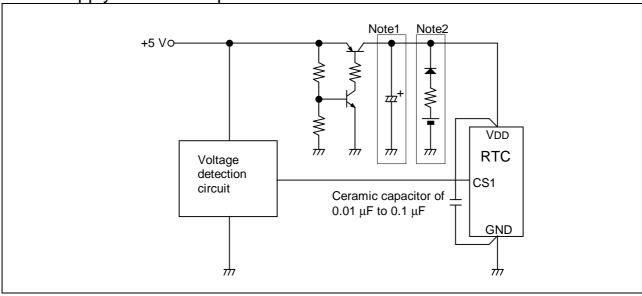

| ■ Power supply circuit example                                                                                                                                                                                                                                                                               | 17             |

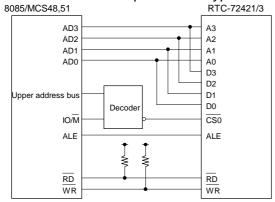

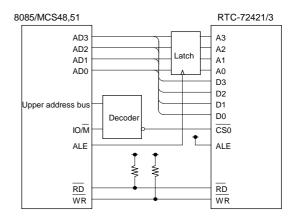

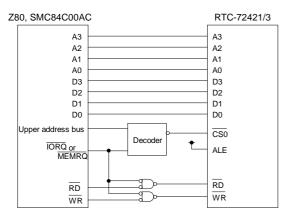

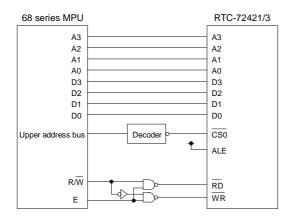

| ■ Examples of connection to general-purpose microprocessor                                                                                                                                                                                                                                                   | 18             |

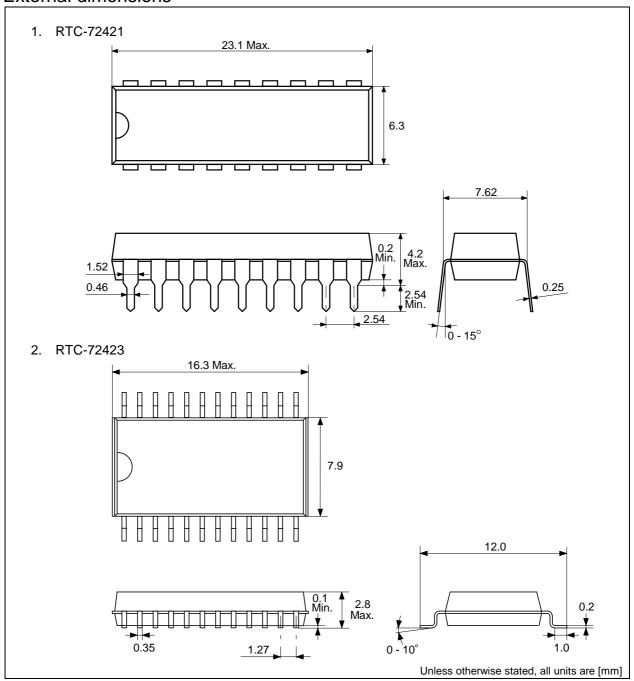

| ■ External dimensions                                                                                                                                                                                                                                                                                        | 19             |

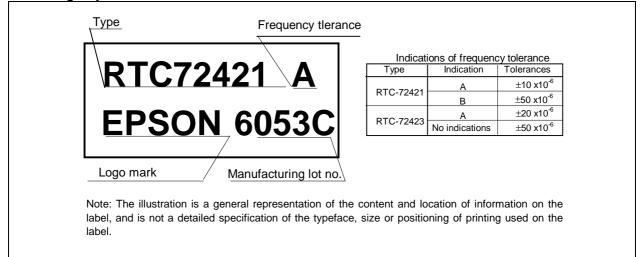

| ■ Marking layout                                                                                                                                                                                                                                                                                             | 19             |

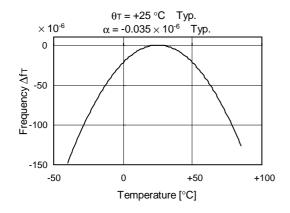

| ■ Reference data                                                                                                                                                                                                                                                                                             | 20             |

| ■ Application notes                                                                                                                                                                                                                                                                                          | 21             |

# 4-BIT PARALLEL INTERFACE REAL TIME CLOCK MODULE

# RTC - 72421 / 72423

- Built-in crystal unit removes need for adjustment and reduces installation costs

- Microprocessor bus compatible (tWW, tRD = 120 ns)

- Use of C-MOS IC enables low current consumption (  $5 \mu A Max.$ , at VDD = 2.0 V )

- Compatibility with Intel CPU bus

- Address latch enable (ALE) pin compatible with multiplex bus CPUs

- Time (hours, minutes, seconds) and calendar (year, month, day) counter

- 24-hour/12-hour switchover and automatic leap-year correction functions

- Fixed-period interrupt function

- 30-seconds correction (adjustment) function

- · Stop, start, and reset functions

- Battery back-up function

- Same mounting conditions as general-purpose SMD ICs possible (RTC-72423)

- \* Pins and functions compatible with the SMC-5242 series

# Overview

The RTC-72421/RTC-72423 module is a real time clock that can be connected directly to a microprocessor's bus. Its built-in crystal unit enables highly accurate time-keeping with no physical access required for adjustment and, since there is no need to connect external components, mounting and other costs can be reduced.

In addition to its time and calendar functions, the RTC-72421/RTC-72423 enables the use of 30-seconds correction and fixed-period interrupt functions.

The RTC-72421/RTC-72423 module is ideally suited for applications requiring timing management, such as personal computers, dedicated word-processors, fax machines, multi-function telephones, and sequencers.

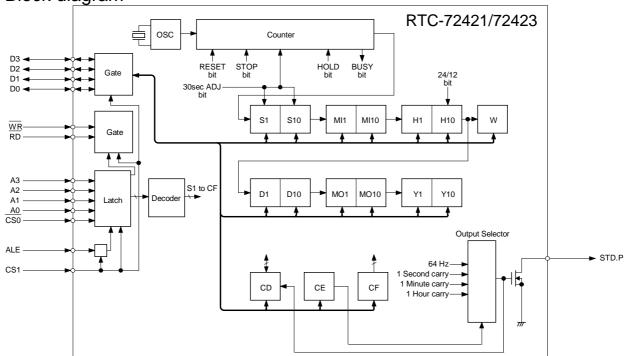

■ Block diagram

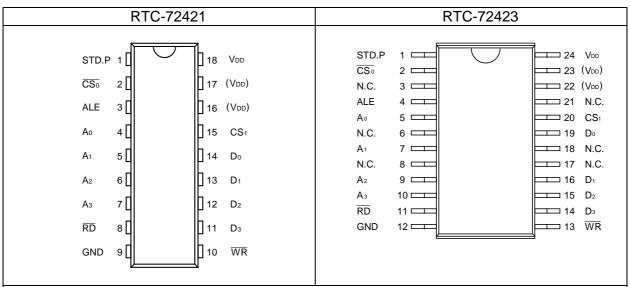

# ■ Terminal connections

The (VDD) pins are at the same electrical level as VDD. Do not connect these pins externally. The N.C. pins are not connected internally. Ground them in order to prevent noise.

# ■ Terminal functions

| Signal                                          |           | No.               | Input/ou  | Function                                                                                                                                                                                                                                                                       |

|-------------------------------------------------|-----------|-------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •                                               | RTC-72421 | RTC-72423         | tput      | Connect these pines to a bi-directional data bus or CPU data bus. Use this bus                                                                                                                                                                                                 |

|                                                 |           |                   |           | to read to and write from the internal counter and registers.                                                                                                                                                                                                                  |

|                                                 |           |                   |           | CS1   CS0   RD   WR   Mode of D0 to D3                                                                                                                                                                                                                                         |

| D <sub>0</sub> -D <sub>3</sub>                  |           |                   | Bi-       | H L L H Output mode (read mode)                                                                                                                                                                                                                                                |

| (Data bus)                                      | 11–14     | 14–16, 19         | direction | H L H L Input mode (write mode)                                                                                                                                                                                                                                                |

| (,                                              |           |                   |           | H L L L Do not use                                                                                                                                                                                                                                                             |

|                                                 |           |                   |           | L H or L High impedance (back-up mode)                                                                                                                                                                                                                                         |

|                                                 |           |                   |           | H H H or L High impedance (RTC not selected)                                                                                                                                                                                                                                   |

| A <sub>0</sub> -A <sub>3</sub><br>(Address bus) | 4–7       | 5, 7, 9, 10       | Input     | Address input pins used for connection to CPU address, etc. Used to select the RTC's internal counter and registers (address selection).  When the RTC is connected to a multiplexed-bus type of CPU, these pines can also be used in combination with the ALE described below |

|                                                 |           |                   |           | Reads in address data and cs state for internal latching.                                                                                                                                                                                                                      |

|                                                 |           |                   |           | When the ALE is high, the address data and CS0 state is read into the RTC.                                                                                                                                                                                                     |

|                                                 |           |                   |           | When the (through-mode) ALE falls, the address data and $\overline{cs_0}$ state at that                                                                                                                                                                                        |

|                                                 |           |                   |           |                                                                                                                                                                                                                                                                                |

| ALE                                             | 3         | 4                 | Input     | point are held. The held address data and cso status are maintained while                                                                                                                                                                                                      |

| (Address Latch Enable)                          |           |                   |           | the ALE is low.                                                                                                                                                                                                                                                                |

|                                                 |           |                   |           | ALE Address data and CSo status  H Read into the RTC to set address data                                                                                                                                                                                                       |

|                                                 |           |                   |           | L Held in the RTC (latched at the trailing edge of the ALE)                                                                                                                                                                                                                    |

|                                                 |           |                   |           | If the RTC is connected to a CPU that does not have an ALE pin and thus there                                                                                                                                                                                                  |

|                                                 |           |                   |           | is no need to use this ALE pin, fix it to VDD.                                                                                                                                                                                                                                 |

|                                                 |           |                   |           | Writes the data on D0 to D3 into the register of the address specified by A0 to                                                                                                                                                                                                |

| WR                                              | 10        | 13                | Input     | A3, at the leading edge of WR.                                                                                                                                                                                                                                                 |

| (WRite)                                         |           |                   |           | Make sure that RD and WR are never low at the same time.                                                                                                                                                                                                                       |

|                                                 |           |                   |           | Output data to D0 to D3 from the register at the address specified by A0 to A3,                                                                                                                                                                                                |

| RD                                              | 8         | 11                | Input     | while RD is low.                                                                                                                                                                                                                                                               |

| (ReaD)                                          | ٥         | 11                | Input     | Make give that an and we are nover law at the same time                                                                                                                                                                                                                        |

| ( 227 )                                         |           |                   |           | Make sure that RD and WR are never low at the same time.                                                                                                                                                                                                                       |

|                                                 |           |                   |           | When CS1 is high and CS0 is low, the RTC's chip-select function is valid and                                                                                                                                                                                                   |

|                                                 |           |                   |           | read and write are enabled.                                                                                                                                                                                                                                                    |

| CS <sub>1</sub> , CS <sub>0</sub>               |           |                   |           | When the RTC is connected to a multiplexed-bus type of CPU, cso requires                                                                                                                                                                                                       |

|                                                 | 15,2      | 20,2              | Input     | the operation of the ALE (see the description of the ALE).                                                                                                                                                                                                                     |

| (Chip Select)                                   |           |                   |           | Use CS1 connected to a power voltage detection circuit. When CS1 is high, the                                                                                                                                                                                                  |

|                                                 |           |                   |           | RTC is enabled; when it is low, the RTC is on standby.  When CS1 goes low, the HOLD and RESET bits in the RTC registers are                                                                                                                                                    |

|                                                 |           |                   |           | cleared to 0.                                                                                                                                                                                                                                                                  |

|                                                 |           |                   |           | This is an N-channel open drain output pin.                                                                                                                                                                                                                                    |

|                                                 |           |                   |           | Depending on the setting of the CE register, a fixed-period interrupt signal and a                                                                                                                                                                                             |

|                                                 |           |                   |           | pulse signal are output.                                                                                                                                                                                                                                                       |

|                                                 |           |                   |           | The output from this pin cannot be inhibited by the CS <sub>1</sub> and CS <sub>0</sub> signals.                                                                                                                                                                               |

|                                                 |           |                   |           | Use a load voltage that is less than or equal to VDD. If not using this pin, keep it                                                                                                                                                                                           |

|                                                 |           |                   |           | open-circuit. An example of STD.P connection is shown below.                                                                                                                                                                                                                   |

|                                                 |           |                   |           | +5 V or VDD                                                                                                                                                                                                                                                                    |

| CTD D                                           |           |                   |           | RTC                                                                                                                                                                                                                                                                            |

| STD.P<br>(STanDard Pulse)                       | 1         | 1                 | Output    | S At least 2.2 kΩ                                                                                                                                                                                                                                                              |

| (STAILDAIGT GISE)                               |           |                   |           |                                                                                                                                                                                                                                                                                |

|                                                 |           |                   |           | STD.P                                                                                                                                                                                                                                                                          |

|                                                 |           |                   |           |                                                                                                                                                                                                                                                                                |

|                                                 |           |                   |           | <u> </u>                                                                                                                                                                                                                                                                       |

|                                                 |           |                   |           | If the STD.P output is not be used during standby operation, connecting the pull-                                                                                                                                                                                              |

|                                                 |           |                   |           | up resister to +5 V provides a reduction in current consumption. If the STD.P output is to be used even during standby, connect the pull-up resistor to the                                                                                                                    |

|                                                 |           |                   |           | RTC's VDD. In this case, the current consumption will be increased by the                                                                                                                                                                                                      |

|                                                 |           |                   |           | amount of current flowing through the pull-up resistor.                                                                                                                                                                                                                        |

| VDD                                             | 18        | 24                |           | Connect this pin to power source. Supply to 5 V $\pm$ 10 % to this pin during normal                                                                                                                                                                                           |

|                                                 |           |                   | 1         | operation; at least 2 V during battery back-up operation.                                                                                                                                                                                                                      |

| GND                                             | 9         | 12                | -         | Connect this pin to ground.                                                                                                                                                                                                                                                    |

| (VDD)                                           | 16, 17    | 22,23<br>3, 6, 8, | -         | These pins are connected internally to VDD. Leave them open circuit.                                                                                                                                                                                                           |

| N.C.                                            | _         | 17, 18, 21        |           | These pins are not connected internally. Ground them.                                                                                                                                                                                                                          |

# **■** Characteristics

# 1. Absolute maximum ratings

| Item                | Symbol | Condition | Specification      | Unit |

|---------------------|--------|-----------|--------------------|------|

| Supply voltage      | VDD    | Ta=+25 °C | -0.3 to 7.0        | V    |

| Input voltage       | Vı     | Ta=+25 °C | GND-0.3 to VDD+0.3 | V    |

| Output voltage      | Vo     | Ta=+25 °C | GND-0.3 to VDD+0.3 | V    |

| Ctorogo tomporatura | Тѕтс   | RTC-72421 | −55 to +85         | °C   |

| Storage temperature | 1516   | RTC-72423 | −55 to +125        | °C   |

# 2. Recommended operating conditions

| Item                           | Symbol | Condition               | Specification          | Unit |

|--------------------------------|--------|-------------------------|------------------------|------|

| Supply voltage                 | VDD    |                         | 4.5 to 5.5             | V    |

| Operating temperature TOPR     |        | No condensation         | RTC-72421 ; -10 to +70 | °C   |

| Operating temperature          | TOPR   | No condensation         | RTC-72423 ; -40 to +85 | °C   |

| Data hold voltage              | VDH    |                         | 2.0 to 5.5             | V    |

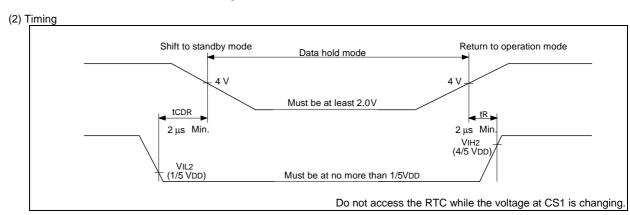

| CS <sub>1</sub> data hold time | tCDR   | See the section on data | 2.0 Min.               |      |

| Operation recovery time        | tr     | hold timing             | 2.0 IVIII1.            | μs   |

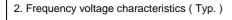

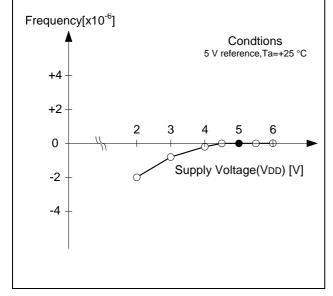

# 3. Frequency characteristics and current consumption characteristics

| Item                              | Symbol   | Condit                                                                | tion                                               | Specif   | ication            | Unit                                  |

|-----------------------------------|----------|-----------------------------------------------------------------------|----------------------------------------------------|----------|--------------------|---------------------------------------|

|                                   |          |                                                                       | RTC-72421A                                         | ± '      | 10                 |                                       |

| Fraguency talarana                | A £ /£ O | Ta=+25 °C                                                             | RTC-72421B                                         | ± ;      | 50                 | ]                                     |

| Frequency tolerance               | Δf/f0    | VDD=5.0 V                                                             | RTC-72423A                                         | ± :      | 20                 |                                       |

|                                   |          |                                                                       | RTC-72423B                                         | ± ;      | 50                 | × 10 <sup>-6</sup>                    |

| Operation to manage up            |          | RTC-72421 : -10 °C to +70 °C (+25 °C reference)                       |                                                    |          | -120               | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| Operation temperature             |          |                                                                       | RTC-72423 : -40 °C to +85 °C<br>(+25 °C reference) |          |                    |                                       |

| Frequency voltage characteristics |          | Ta=+25<br>VDD=2.0 V                                                   | -                                                  | ± 5 N    | Лах.               | $\times$ 10 <sup>-6</sup> / V         |

| Aging                             | fa       | VDD=5.0 V, T                                                          | a=+25 °C                                           | ± 5 l    | <b>Лах</b> .       | × 10 <sup>-6</sup> / year             |

| Shock resistance                  | S.R.     | Drop test 3 times on a 0.75 m height, or 2940 1/2 sin wave × 3 direct | ± 10                                               | Max.     | × 10 <sup>-6</sup> |                                       |

| Current consumption               | IDD1     |                                                                       | VDD=5.0 V                                          | 1.0 Typ. | 10 Max.            | ^                                     |

| Current consumption               | IDD2     | I/O currents excluded                                                 | VDD=2.0 V                                          | 0.9 Typ. | 5 Max.             | μΑ                                    |

# 4. Electrical characteristics ( DC characteristics )

| Item                      | Symbol | Condition          | Applicable pins                                        | Min.   | Тур. | Max.               | Unit |

|---------------------------|--------|--------------------|--------------------------------------------------------|--------|------|--------------------|------|

| High input voltage 1      | VIH1   |                    | All input pins except for                              | 2.2    |      |                    | V    |

| Low input voltage 1       | VIL1   |                    | CS <sub>1</sub>                                        |        |      | 0.8                |      |

| High input voltage 2      | VIH2   | VDD=2.0 V to       | CS <sub>1</sub>                                        | 4/5VDD |      |                    | V    |

| Low input voltage 2       | VIL2   | 5.5 V              | CSI                                                    |        |      | 1/5V <sub>DD</sub> | V    |

| Input leakage current 1   | ILK1   | VI=VDD/0 V         | Input pins except for D <sub>0</sub> to D <sub>3</sub> |        |      | 1/-1               | μΑ   |

| Input leakage current 2   | llk2   |                    |                                                        |        |      | 10/-10             |      |

| Low output voltage 1      | Vol1   | IOL=2.5 mA         | Do to D3                                               |        |      | 0.4                |      |

| High output voltage       | Voн    | ΙΟΗ=-400 μΑ        |                                                        | 2.4    |      |                    | V    |

| Low output voltage 2      | Vol2   | IOL=2.5 mA         | STD.P                                                  |        |      | 0.4                |      |

| Off-state leakage current | IOFFLK | VI = VDD / 0 V     | SID.P                                                  |        |      | 10/-10             | μΑ   |

| Input capacitance         | Cı     | Input<br>frequency | Input pins except for Do to D3                         |        | 10   |                    | pF   |

| Input-output capacitance  | Ci/o   | 1 MHz              | D <sub>0</sub> to D <sub>3</sub> and STD.P             |        | 20   |                    | þΓ   |

# ■ Switching characteristics (AC characteristics)

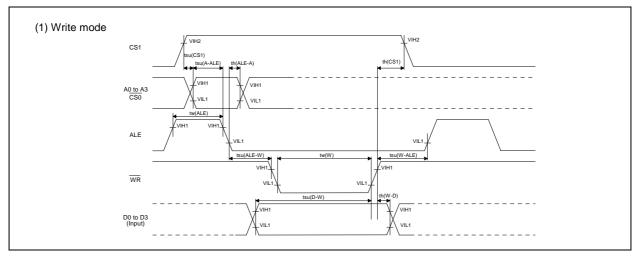

# 1. When ALE is used

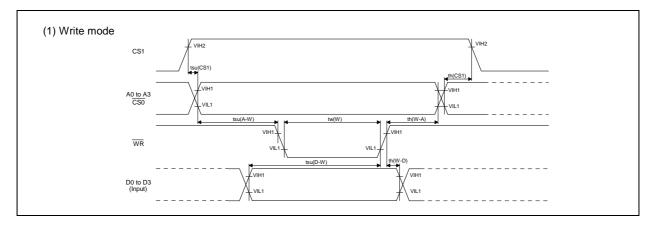

Write mode

Item Condition Max. Unit Symbol Min. CS1 set-up time tsu(CS1) 1000 Address set-up time before ALE tsu(A-ALE) 50

RTC-72421;  $Ta=-10 \, ^{\circ}C$  to +70  $^{\circ}C$ , RTC-72423;  $Ta=-40 \, ^{\circ}C$  to +85  $^{\circ}C$ )

( VDD=5 V  $\pm$  0.5 V,

| Address set up time before ALL      | 100(/ 1 / 122/ | 00   |    |

|-------------------------------------|----------------|------|----|

| Address hold time after ALE         | th(ALE-A)      | 50   |    |

| ALE pulse width                     | tw(ALE)        | 80   |    |

| ALE set-up time before write        | tsu(ALE-W)     | 0    |    |

| Write pulse width                   | tw(W)          | 120  | ns |

| ALE set-up time after write         | tsu(W-ALE)     | 50   |    |

| Data input set-up time before write | tsu(D-W)       | 80   |    |

| Data input hold time after write    | th(W-D)        | 10   |    |

| CS1 hold time                       | th(CS1)        | 1000 |    |

| Write recovery time                 | trec(W)        | 200  |    |

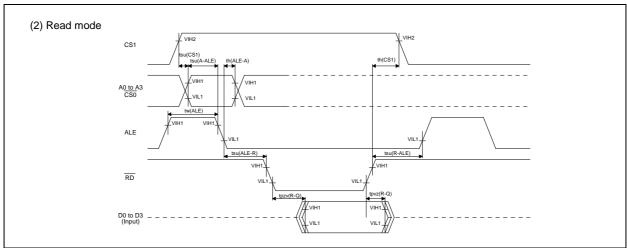

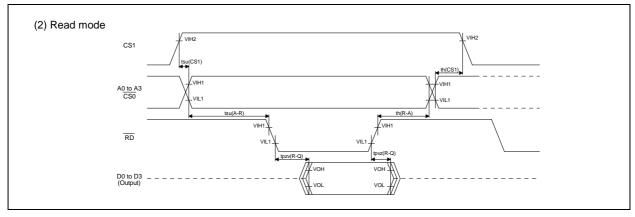

| Read mode (V                                  | $DD=5 V \pm 0.5 V$ , | RTC-72421;Ta=-10 °C | to +70 °C, RTC | -72423;Ta=-40 | °C to +85 °C |

|-----------------------------------------------|----------------------|---------------------|----------------|---------------|--------------|

| Item                                          | Symbol               | Condition           | Min.           | Max.          | Unit         |

| CS1 set-up time                               | tsu(CS1)             |                     | 1000           |               |              |

| Address set-up time before ALE                | tsu(A-ALE)           |                     | 50             |               |              |

| Address hold time after ALE                   | th(ALE-A)            |                     | 50             |               |              |

| ALE pulse width                               | tw(ALE)              |                     | 80             |               |              |

| ALE set-up time before read                   | tsu(ALE-R)           |                     | 0              |               | ns           |

| ALE set-up time after read                    | tsu(R-ALE)           |                     | 50             |               |              |

| Data output transfer time after read          | tPZV(R-Q)            | CL=150 pF           |                | 120           |              |

| Data output floating transfer time after read | tpvz(R-Q)            |                     | 0              | 70            |              |

| CS1 hold time                                 | th(CS1)              |                     | 1000           |               |              |

| Read recovery time                            | trec(W)              |                     | 200            |               |              |

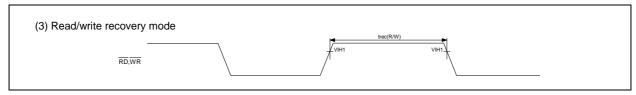

# 2. When ALE is fixed at VDD

| Write mode                          | $(VDD=5 V \pm 0.5 V,$ | RTC-72421;Ta=-10 °C | to +/0 °C, RTC | -72423;1a=-40° | C to +85 °C |

|-------------------------------------|-----------------------|---------------------|----------------|----------------|-------------|

| Item                                | Symbol                | Condition           | Min.           | Max.           | Unit        |

| CS1 set-up time                     | tsu(CS1)              |                     | 1000           |                |             |

| CS1 hold time                       | th(CS1)               |                     | 1000           |                |             |

| Address set-up time before write    | tsu(A-W)              |                     | 50             |                |             |

| Address hold time after write       | th(W-A)               |                     | 10             |                | ns          |

| Write pulse width                   | tw(W)                 |                     | 120            |                |             |

| Data input set-up time before write | tsu(D-W)              |                     | 80             |                |             |

| Data input hold time after write    | th(W-D)               |                     | 10             |                |             |

| Write recovery time                 | trec(W)               |                     | 200            |                |             |

| Read mode (                                  | VDD=5 V $\pm$ 0.5 V, | RTC-72421;Ta=-10 °C | C to +70 °C, RTC | 5-72423;Ta=-40 | °C to +85 °C |

|----------------------------------------------|----------------------|---------------------|------------------|----------------|--------------|

| Item                                         | Symbol               | Condition           | Min.             | Max.           | Unit         |

| CS1 set-up time                              | tsu(CS1)             |                     | 1000             |                |              |

| CS1 hold time                                | th(CS1)              |                     | 1000             |                |              |

| Address set-up time before read              | tsu(A-R)             |                     | 50               |                |              |

| Address hold time after read                 | th(R-A)              |                     | 10               |                | ns           |

| Data output transfer time after read         | tpzv(R-Q)            | CL=150 pF           |                  | 120            |              |

| Data output floating transfer time after rea | ad tpvz(R-Q)         |                     | 0                | 70             |              |

| Read recovery time                           | trec(R)              |                     | 200              |                |              |

# ■ Registers

### 1. Register table

| Address | А3 | A2 | A2 A1 A0 |    | Register |         | Da       | ata            |       | Count      | Remarks                   |

|---------|----|----|----------|----|----------|---------|----------|----------------|-------|------------|---------------------------|

| (Hex)   | AS | AZ | AI       | Α0 | name     | D3      | D2       | D1             | D0    | (BCD)      | Remarks                   |

| 0       | 0  | 0  | 0        | 0  | S1       | s8      | s4       | s2             | s1    | 0 to 9     | 1-second digit register   |

| 1       | 0  | 0  | 0        | 1  | S10      | *       | s40      | s20            | s10   | 0 to 5     | 10-seconds digit register |

| 2       | 0  | 0  | 1        | 0  | MI1      | mi8     | mi4      | mi2            | mi1   | 0 to 9     | 1-minute digit register   |

| 3       | 0  | 0  | 1        | 1  | MI10     | *       | mi40     | mi20           | mi10  | 0 to 5     | 10-minute digit register  |

| 4       | 0  | 1  | 0        | 0  | H1       | h8      | h4       | h2             | h1    | 0 to 9     | 1-hour digit register     |

| 5       | 0  | 1  | 0        | 1  | H10      | *       | PM/AM    | h20            | h10   | 0 to1 or 2 | 10-hours digit register   |

| 6       | 0  | 1  | 1        | 0  | D1       | d8      | d4       | d2             | d1    | 0 to 9     | 1-day digit register      |

| 7       | 0  | 1  | 1        | 1  | D10      | *       | *        | d20            | d10   | 0 to 3     | 10-days digit register    |

| 8       | 1  | 0  | 0        | 0  | MO1      | mo8     | mo4      | mo2            | mo1   | 0 to 9     | 1-month digit register    |

| 9       | 1  | 0  | 0        | 1  | MO10     | *       | *        | *              | mo10  | 0 to 1     | 10-months digit register  |

| Α       | 1  | 0  | 1        | 0  | Y1       | y8      | y4       | y2             | y1    | 0 to 9     | 1-year digit register     |

| В       | 1  | 0  | 1        | 1  | Y10      | y80     | y40      | y20            | y10   | 0 to 9     | 10-years digit register   |

| С       | 1  | 1  | 0        | 0  | W        | *       | w4       | w2             | w1    | 0 to 6     | Day-of-the-week register  |

| D       | 1  | 1  | 0        | 1  | CD       | 30s ADJ | IRQ FLAG | BUSY           | HOLD  |            | Control register D        |

| E       | 1  | 1  | 1        | 0  | CE       | t1      | tO       | ITRPT/<br>STND | MASK  |            | Control register E        |

| F       | 1  | 1  | 1        | 1  | CF       | TEST    | 24/12    | STOP           | RESET |            | Control register F        |

#### 2. Notes

The counts at addresses 0 to C are all positive logic. Therefore, a register bit that is 1 appears as a high-level signal on the data bus. Data representation is BCD.

Do not set an impossible date or time in the RTC. If such a value is set, the effect is unpredictable.

When the power is turned on (before the RTC is initialized), the state of all bits is undefined. Therefore, write to all registers after power-on, to set initial values. For details of the initialization procedure, see "Using the RTC-72421/RTC-72423".

The TEST bit of control register F is used by EPSON for testing. Operation cannot be guaranteed if 1 is written to this bit, so make sure that it is set to 0 during power-on initialization.

#### 3. Functions of register bits (overview)

| Bit name              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| * mark                | ot used. Writing to this bit has no effect; reading it always returns 0.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Seconds to year digit | All written BCD code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Day-of-the-week digit | This is special (base 7) counter that increments each time the day digits are incremented. It counts from 0 to 6. Since the value in the counter bears no relationship to the day of the week, the user can choose the coding that relates the counter value to the day of the week. The following is just one example of this relationship.    Count                                                                                                                                    |  |  |  |  |  |  |  |

| PM/AM                 | The PM/AM bit is 1 for p.m. times; 0 for a.m. times. This bit is valid only for 12-hour-clock mode (when the 24/12 bit is 0); in 24-hour-clock mode (when the 24/12 bit is 1), this bit is always 0.                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 30-seconds ADJ        | Writing 1 to this bit executes a 30-seconds correction.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| IRQ FLAG              | The IRQ FLAG bit is set to 1 when an interrupt request is generated in fixed-period interrupt mode. Writing 0 to this bit clears it. Note that it is possible to write 1 to this bit, but this will have no effect.  In fixed-period pulse output mode, this bit is at 1 while the pulse output is active(While the STD.P pin output is low), and is automatically cleared when pulse output ends. Writing 0 to this bit while pulse output is active forcibly cancels the pulse output. |  |  |  |  |  |  |  |

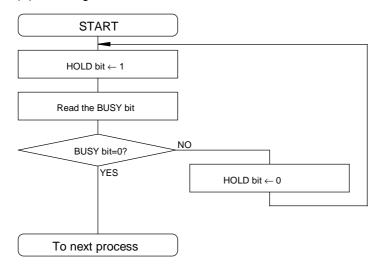

| BUSY                  | Use the BUSY bit when accessing data in the S1 to W registers. This bit is set to 1 during the incrementation cycle of the S1 to W registers, and is set to 0 otherwise. When the BUSY bit is 1, access to the S1 to W registers is inhibited.  Note that the HOLD bit must also be used when accessing the S1 to W registers. The BUSY bit is always 1 when the HOLD bit is 0. There is no need to check the BUSY bit when accessing the control registers (CD, CE and CF).             |  |  |  |  |  |  |  |

| HOLD                  | When 1 has been written to the HOLD bit, the status of the BUSY bit can be checked. While the HOLD bit is 1, any incrementation of the digits is held just once. (The incrementation is held only once, even if the HOLD bit remains at 1 for two or more seconds.)  Clear the HOLD bit to 0 by forcing the CS1 pin low.                                                                                                                                                                 |  |  |  |  |  |  |  |

| t1,t0                 | These bits set the timing for fixed-period pulse output and interrupts (1/64 seconds, 1 second, 1minute or 1 hour).                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| ITRPT/STND            | The ITRPT/STND bit sets fixed-period pulse output mode and fixed-period interrupt mode. Write 1 to this bit to set interrupt(INRPT) mode; when write 0 to it to set pulse output(STND) mode.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| MASK                  | The MASK bit disables fixed-period pulse output and fixed-period interrupts. Write 1 to this bit to mask and inhibit these modes; write 0 to it to enable these modes.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| TEST                  | The TEST bit is used by EPSON for test purposes. Operation cannot be guaranteed if 1 is written to this bit, so make sure that it is set to 0 during power-on initialization.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 24/12                 | The 24/12 bit switches between 24-hour clock and 12-hour clock. Write 1 to this bit to set 24-hour mode; write 0 to it to set 12-hour mode. When the 24/12 bit is set, both the timer registers and the timer mode must be reset to match. Note that the h20 bit of the H10 register is always in 12-hour-clock mode.                                                                                                                                                                    |  |  |  |  |  |  |  |

| STOP                  | The STOP bit sets an inhibition on clock operation in 8192 Hz steps which are divisions of the 1 second signal from the RTC's internal 32768 Hz oscillation source. The clock is inhibited when the STOP bit is 1, and released again when it becomes 0. The internal oscillation circuit continues to operate even when the STOP bit is 1.                                                                                                                                              |  |  |  |  |  |  |  |

| RESET                 | The RESET bit resets the part of the counter that is below one second. Write 1 to this bit to reset; 0 to release the reset.  The RESET bit set to 0 when the CS1 pin goes low.                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

# 4. Setting the fixed-period pulse output mode and fixed-period interrupt mode

| Mode                                | MASK | ITRPT/STND | ITRPT/STND    | STD.P pin    |

|-------------------------------------|------|------------|---------------|--------------|

| Fixed-period pulse output mode      | 0    | 0          | Set to 1 when | Set low when |

| Fixed-period interrupt mode         | 0    | 1          | active        | active       |

| Fixed-period pulse output inhibited | 1    | 0 or 1     | "0"           | Open-circuit |

|               | Setting of fixed-period output timing |     |        |        |

|---------------|---------------------------------------|-----|--------|--------|

| t1 bit        | 0                                     | 0   | 1      | 1      |

| t0 bit        | 0                                     | 1   | 0      | 1      |

| Output period | 1/64 s                                | 1 s | 1 min. | 1 hour |

# 5. Resetting the fixed-period pulse output mode and fixed-period interrupt mode

| Mode                                  | IRQ FLAG | IRQ FLAG                                                         | STD.P pin                                                                  |

|---------------------------------------|----------|------------------------------------------------------------------|----------------------------------------------------------------------------|

| Fixed-period pulse output mode        | write 0  | Reset immediately after the write $("1" \rightarrow "0")$        | Reset immediately after the write $(\text{"L"} \rightarrow \text{"OPEN"})$ |

| MASK=0<br>ITRPT/STND=0                | No write | Automatically returned by the set period $("1" \rightarrow "0")$ | Automatically returned by the set period $(\text{"L"} \to \text{"OPEN"})$  |

| Fixed-period interrupt mode<br>MASK=0 | write 0  | Reset immediately after write $("1" \rightarrow "0")$            | Reset immediately after the write $(\text{"L"} \rightarrow \text{"OPEN"})$ |

| ITRPT/STND=1                          | No write | The interrupt request continues, with no                         | reset. Subsequent interrupt are ignored.                                   |

# Register description

#### 1. Timing registers

#### (1) S1 to Y10 registers

These registers are 4-bit, positive logic registers in which the digits of the year, month, day, hour, minute, and second are continuously written in BCD code.

For example, when(1, 0, 0, 1) has been written to the bits of the S1 register, the current value in the S1 register is 9. As described previously, data is handled by 4-bit BCD codes. Therefore, the S1 to Y10 registers consist of units registers and tens registers.

When seconds are read, for example, the values in the S1 and S10 registers are both read out to give the total number of seconds

#### (2) W register

The W register is a counter that increments each time the day digits are incremented. It counts from 0 to 6. Since the value in the counter bears no relationship to the day of the week, the user can choose the coding that relates the counter value to the day of the week. The following is just one example of this relationship;

| Count | 0      | 1      | 2       | 3         | 4        | 5      | 6        |

|-------|--------|--------|---------|-----------|----------|--------|----------|

| Day   | Sunday | Monday | Tuesday | Wednesday | Thursday | Friday | Saturday |

#### (3) H10 register (PM/AM, h20, h10)

The H10 register contains a combination of the 10-hours digit bits and the PM/AM bit. Therefore, the contents of this register will depend on whether the 12-hour clock or 24-hour clock is selected. If the 12-hour clock is selected, the user must bear in mind that this register will contain two types of data: 10-hour data in the h10 bit and a.m./p.m. data in the PM/AM bit. The PM/AM bit is 0 for a.m. and 1 for p.m.

For example, if a value of 48 is obtained from the H10 and H1 registers when the H10, H1, M10, and M1 registers are read, remember that the inclusion of a set PM/AM bit (PM/AM=1) will make the tens digit appear to be 4. Since this bit is 1, the time is p.m. If the value read from the M10 and M1 registers is 00, the actual time should be read as 8:00 p.m.

Similarly, if the value read from the H10 and H1 registers is 11, the PM/AM bit is 0, and so this time is therefore a.m. If the value read from the M10 and M1 registers is 30, this time should be read as 11:30 a.m.

When the 12-hour clock is used, the h20 bit should never be 1, but it is nonetheless physically possible to write a 1 in this bit. The user should be careful to write a 0, to avoid unpredictable consequences. Note that, if a mistake in the PM/AM value is made while in 12-hour-clock mode, the date digits will be half a day out. Correct setting is needed. If the 24-hour clock is selected, the PM/AM bit will always be 0.

For details of how to set 12-hour or 24-hour clock, see the section on the 24/12 bit.

| Setting       | Possible times                |  |

|---------------|-------------------------------|--|

| 12-hour clock | 12:00 to 11:59, a.m. and p.m. |  |

| 24-hour clock | 00:00 to 23:59                |  |

#### (4) Y1 and Y10 registers

The Y1 and Y10 registers can handle the last two digits of the year in the Gregorian calendar. Leap years are automatically identified, and this affects the handling of the month and day digits for February 29.

#### [Leap years]

In general, a year contains 365 days. However, the Earth takes slightly longer than exactly 365 days to rotate around the sun, so we need to set leap years in compensation. A leap year occurs once every four years, in years in the Gregorian calendar that are divisible by four. However, a further small correction is necessary in that years that are divisible by 100 are ordinary years, but years that are further divisible by 400 are leap years.

The main leap and ordinary years since 1900 and into the future are listed on the right.

#### [ Leap years in the RTC-72421/72423 ]

To identify leap years, the RTC-72421/RTC-72423 checks whether or not the year digits are divisible by four. As implied above, 2000 will be a leap year, and so no further correction will be necessary in that case.

This process identifies the following years as leap years:

96, (20)00, (20)04, (20)08, (20)12.

The turn-of-the-century years for which the RTC-72421/RTC-72423 will require a correction are shown shaded in the table on the right.

If Japanese-era years are set, accurate leap-year identification will only be possible if the era years that are divisible by four are actually leap years. As it happens, years in the current era, Heisei, that are divisible by four are leap years, which means that Heisei years can be set in these registers.

| Actual leap years and ordinary years |           |          |  |  |

|--------------------------------------|-----------|----------|--|--|

| Year                                 | Leap year | Ordinary |  |  |

|                                      |           | year     |  |  |

| 1900                                 |           | О        |  |  |

| :                                    |           |          |  |  |

| 1993                                 |           | О        |  |  |

| 1994                                 |           | О        |  |  |

| 1995                                 |           | 0        |  |  |

| 1996                                 | 0         |          |  |  |

| 1997                                 |           | О        |  |  |

| 1998                                 |           | 0        |  |  |

| 1999                                 |           | О        |  |  |

| 2000                                 | 0         |          |  |  |

| 2001                                 |           | 0        |  |  |

| 2002                                 |           | О        |  |  |

| 2003                                 |           | О        |  |  |

| 2004                                 | 0         |          |  |  |

| 2005                                 |           | О        |  |  |

| :                                    |           |          |  |  |

| 2100                                 |           | 0        |  |  |

| 2200                                 |           | О        |  |  |

| 2300                                 |           | О        |  |  |

| 2400                                 | 0         |          |  |  |

|                                      |           |          |  |  |

#### (5) Out-of-range data

If an impossible date or time is set, this may cause errors. If such a date is set, the behavior of the device is in general unpredictable, so make sure that impossible data is not set.

#### 2. CD register (control register D)

#### (1) HOLD bit (D0)

Use the HOLD bit when accessing the S1 and W registers. For details, see "Read/write of S1 to W registers".

| HOLD bit | Function HOLD bit                                                                                          |

|----------|------------------------------------------------------------------------------------------------------------|

| 0        | The BUSY bit is always 1 (the BUSY status cannot be checked).                                              |

| 1        | The BUSY status can be checked. When the HOLD bits is 1 and the BUSY bit is 0, read and write are enabled. |

When the HOLD bit is 1, any incrementation in the count is held within the RTC. The held incrementation is automatically compensated for when the HOLD bit becomes 0. (Second and subsequent incrementations are ignored.) Therefore, if the HOLD bit is at 1 for two or more seconds in succession, the time will be slightly slow (delay). Make sure that any access to the S1 to W registers is completed within one second, then clear the HOLD bit to 0.

The status of the BUSY bit remains as set while the HOLD bit is at 1. If the HOLD bit is not cleared temporarily to 0, the BUSY bit will not indicate any change within the RTC of the BUSY status. Therefore, when checking the status of the BUSY bit, write 0 to the HOLD bit each time the BUSY bit is read, to update the status of the BUSY bit.

If the CS1 pin goes low while the HOLD bit is 1, the HOLD bit is automatically cleared to 0.

There is no need to use the HOLD bit when accessing the control registers (CD, CE, and CF).

#### (2) BUSY bit (D1)

The BUSY bit indicates whether or not the digits from the seconds digit onward are being incremented, and is used when accessing the S1 to W registers. For details, see "Read/write of S1 to W registers".

There is no need to check the BUSY bit when accessing the control registers (CD, CE, and CF).

| BUSY bit | Significance of the BUSY bit | Condition | Remarks                                                 |

|----------|------------------------------|-----------|---------------------------------------------------------|

| 0        | Access enable                | HOLD=1    | The RTC is not counting                                 |

| 1        | Access disabled              |           | The count has been incremented in the RTC (190 μs Max.) |

| 1        | BUSY is always 1             | HOLD=0    | The count cannot be checked                             |

The status of the BUSY bit remains as set while the HOLD bit is at 1. If the HOLD bit is not cleared temporarily to 0, the BUSY bit will not indicate any change within the RTC of the BUSY status. Therefore, when checking the status of the BUSY bit, write 0 to the HOLD bit each time the BUSY bit is read, to update the status of the BUSY bit. The BUSY bit is a read-only bit, so any attempt to write 1 or 0 to it is ignored.

#### (3) IRQ FLAG bit (D2)

The IRQ FLAG bit is an internal status bit that corresponds to the status of the STD.P pin output, to indicate whether or not an interrupt request has been issued to the CPU. When the STD.P pin output is low, the IRQ FLAG bit is 1; when the STD.P pin output is open-circuit, the IRQ FLAG bit is 0.

When writing data to the CD register, keep the IRQ FLAG bit at 1, except when deliberately writing 0 to it. Writing 0 to the IRQ FLAG bit cancels its status if it had become 1 at that instant or just before.

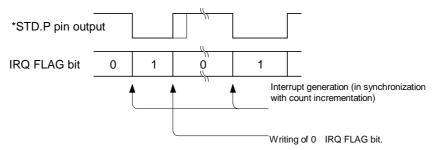

#### i. Interrupt processing (interrupt status monitor function)

Since the IRQ FLAG bit indicates that an interrupt request has been generated to the CPU, it is in synchronization with the status of the STD.P pin output. In other words, the status of the STD.P pin output can be monitored by monitoring the IRQ FLAG bit.

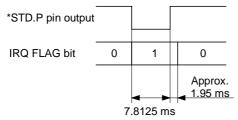

In fixed-period pulse output mode, the relationship between the IRQ FLAG bit and the STD.P pin output is as follows:

| STD.P pin output            | IRQ FLAG bit |

|-----------------------------|--------------|

| Low                         | 1            |

| Open(for open-drain output) | 0            |

The timing of the IRQ FLAG bit and the STD.P pin output in fixed-period pulse output mode is as follows:

The output levels of the STD.P pin are low (down) and open circuit (up).

#### ii. STD.P pin output reset function

The STD.P pin output can be reset after an interrupt is generated by writing 0 to the IRQ FLAG bit.

The relationships of this operation are shown below. Note that writing 1 to this bit is possible, but it has no effect.

| IRQ FLAG bit | STD.P pin output            |

|--------------|-----------------------------|

| 1            | Low                         |

| 0            | Open(for open-drain output) |

The output levels of the STD.P pin are low (down) and open circuit (up).

Note: If the STD.P pin output remains low as set, subsequently generated interrupts are ignored. In order to prevent interrupts from being overlooked, write 0 to the IRQ FLAG bit before the next interrupt is generated, to return the STD.P pin to high.

#### iii. Initial setting of IRQ FLAG bit

If the fixed-period interrupt mode is not used, set the IRQ FLAG bit to 1. If the fixed-period interrupt mode is used, set the IRQ FLAG bit to 0.

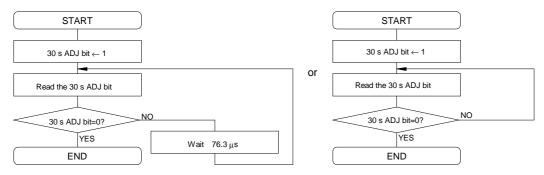

#### (4) 30-second ADJ bit (D3)

The 30-seconds ADJ bit provides a 30-seconds correction (by which term is meant a rounding to the nearest whole minute) when 1 is written to it. The 30-seconds correction takes a maximum of  $76.3~\mu s$  to perform, and after the correction the 30-seconds ADJ bit is automatically returned to 0. This operation also clears the sub-second bits of the internal counter down to the 1/256-seconds counter. During the 30-seconds correction, access to the counter registers at addresses 0 to C is inhibited, so monitor the 30-seconds ADJ bit to check that this bit has returned to 0, before starting subsequent processing. If no access is made to the RTC for  $76.3~\mu s$  or more after 1 is written to the 30-seconds ADJ bit, there is no need to check the 30-seconds ADJ bit again.

#### i. Operation of 30-seconds ADJ bit

Writing 1 to the 30-seconds ADJ bit performs a 30-second correction. This 30-seconds correction changes the seconds and minutes digits as shown below. If the minutes digits have been incremented, an upward carry is propagated.

| Status of seconds digits before correction                   | Status of seconds digits after correction |

|--------------------------------------------------------------|-------------------------------------------|

| Up to 29 seconds 00 seconds. No carry to the minutes digits. |                                           |

| 30 to 59 seconds 0 seconds. Carry to the minutes digits.     |                                           |

Example: The correction caused by the 30-seconds ADJ bit sets the time within the RTC to 00:00:00 if it was within the range of 00:00:00 to 00:00:29, or to 00:01:00 if it was within the range of 00:00:30 to 00:00:59.

#### ii. Access inhibited after 30-seconds correction

For 76.3  $\mu$ s after 1 is written to the 30-seconds ADJ bit, the RTC is engaged in internal processing, so read to and write from the S1 to W registers is inhibited. The 30-seconds ADJ bit is automatically cleared to 0 at the end of the 76.3  $\mu$ s.

# 3. CE register (control register E)

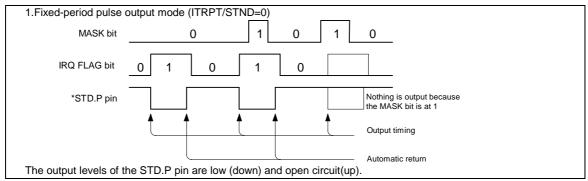

#### (1) MASK bit (D0)

The MASK bit controls the STD.P pin output. The relationships between the MASK bit, ITRPT/STND bit, and STD.P pin output are as follows:

|      | •••        |                                |

|------|------------|--------------------------------|

| MASK | ITRPT/STND | STD.P pin output               |

| 0    | 0          | Fixed-period pulse output mode |

| 0    | 1          | Fixed-period interrupt mode    |

| 1    | 0 or 1     | Open                           |

The timings of the MASK bit, ITRPT/STND bit, and STD.P pin output are as follows:

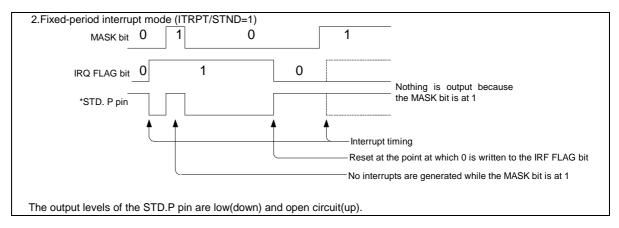

#### (2) ITRPT/STND bit (D1)

The ITRPT/STND bit specifies fixed-period pulse output mode or fixed-period interrupt mode for the fixed-period operating mode.

The mode selected by each setting of this bit is as follows:

| , ,        |                                |

|------------|--------------------------------|

| ITRPT/STND | Operating mode                 |

| 0          | Fixed-period pulse output mode |

| 1          | Fixed-period interrupt mode    |

For details of the timing of fixed-period operation, see the section on the t0 and t1 bits below.

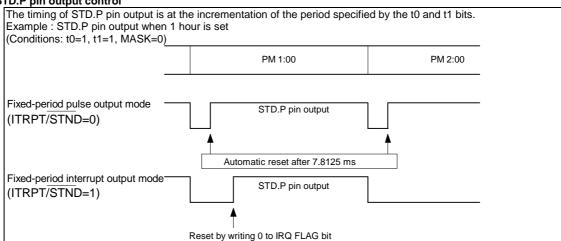

#### (3) t0 (D2), t1 (D3) bits

These bits select the timing of fixed-period operation in fixed-period pulse output mode or fixed-period interrupt mode. There is no special counter within the RTC for fixed-period operation; the fixed-period operation is performed at the incrementation of the time (period) specified by the t0 and t1 bits.

#### i. Setting t0 and t1

Setting these bits specifies the generation timing for fixed-period pulse output or fixed-period interrupts.

| t1 | t0 | Period(frequency)    | Remarks                                                        |

|----|----|----------------------|----------------------------------------------------------------|

| 0  | 0  | 1/64 seconds (64 Hz) | In fixed-period pulse output mode, the STD.P pin output is low |

| 0  | 1  | 1 second (1 Hz)      | for 7.8125 ms                                                  |

| 1  | 0  | 1 minute (1/60 Hz)   | (not that half the 1/64 second period is 7.8125 ms)            |

| 1  | 1  | 1 hour (1/3600 Hz)   |                                                                |

#### ii. STD.P pin output control

#### iii. Frequency of STD.P pin output in fixed-period pulse output mode

In fixed-period pulse output mode, the timing of output is determined by the frequency of the internal crystal unit. This means that the output can be used to measure any error in the frequency of the crystal unit.

Note: The 30-seconds correction could generate a carry. If such a carry occurs when the t0 and t1 bits are set to (0, 1) or (1, 1), the STD.P pin output could end up low. If the ITRPT/STND bit is 0, this low-level STD.P pin output will be held from the time that the part of the counter that is below one second is cleared by the 30-seconds correction until the incrementation of the 1/64-second digit of the internal counter restarts. Note that this may be different from the normal case in which the STD.P pin output is low for 7.8125 ms.

The time of the low-level output of the first STD.P pin output after a RESET or STOP operation, or after 1 has been written to the IRQ FLAG bit, may not be 7.8125 ms.

If any one of the t0, t1, or ITRPT/STND bits is overwritten, the IRQ FLAG bit may become 1. Therefore, after writing to any of these bits, it is necessary to first write 0 to the IRQ FLAG bit then wait until the IRQ FLAG bit changes back to 1.

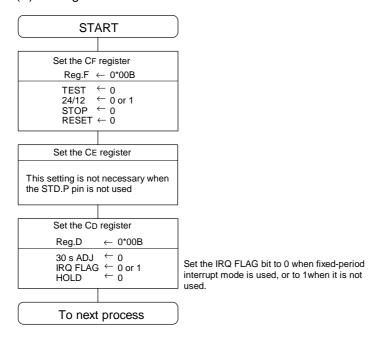

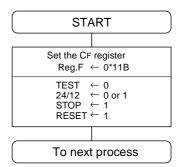

#### 4. CF register (control register F)

#### (1) RESET bit (D0)

Writing 1 to the RESET bit clears the sub-second bits of the internal counter down to the 1/256-seconds counter. The reset continues for as long as the RESET bit is 1. End the reset by writing 0 to the RESET bit. If the level of the CS1 pin goes low, the RESET bit is automatically cleared to 0.

#### (2) STOP bit (D1)

Writing 1 to the STOP bit stops the clock of the internal counter from the 1/8192 second bit onward. Writing 0 to the STOP bit restarts the clock.

This function can be used to create a cumulative timer.

#### (3) 24/12 bit (D2)

Set the 24/12 bit to select either 12-hour clock or 24-hour clock as the timer mode. In 12-hour clock mode, the PM/AM bit is used.

#### i. Switching between 12-hour clock and 24-hour clock

Writing 1 to the 24/12 bit selects 24-hour clock mode. In 24-hour clock mode, the PM/AM bit is inoperative and is always 0. Writing 0 to the 24/12 bit selects 12-hour clock mode. In 12-hour clock mode, the PM/AM bit becomes valid. It is 0 for a.m. times and 1 for p.m. times.

#### ii. Overwriting the 24/12 bit

Overwriting the contents of the 24/12 bit could destroy the contents of the registers from the H1 register upward (from the 1-hour digit upward). Therefore, before overwriting the 24/12 bit, it is necessary to save the contents of the hour (H1, H10), day (D1, D10), month (MO1, MO10), year (Y1, Y10), and day-of-the-week (W) registers, then re-write the data back into the registers to suit the new timer mode, after overwriting the 24/12 bit.

#### (4) TEST bit (D3)

The TEST bit is used by EPSON for test purposes. Operation cannot be guaranteed if 1 is written to this bit, so make sure that it is set to 0 during power-on initialization.

# ■ Using the RTC-72421/RTC-72423

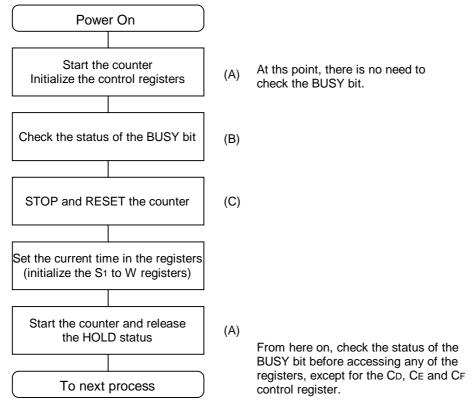

### 1. Power-on procedure (initialization)

When power is turned on, the contents of all registers and the output from the STD.P pin are undefined. Therefore, all the registers must be initialized after power on. Follow the procedure given below for initialization.

For details of processes (A) to (C), see next page.

# (A)Starting the count

# (B)Checking the status of the BUSY bit

### (C)Stopping and resetting the counter

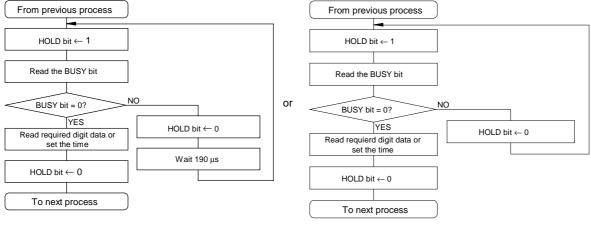

### 2. Read/write of S1 to W registers

Use one of the procedures shown below to access registers other than the control registers (CD, CE, and CF) while the RTC is operating. Note that the control registers can be accessed regardless of the status of the BUSY bit.

Read or write when the HOLD bit is used

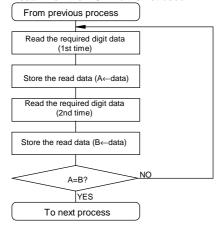

#### Read when the HOLD bit is not used

The operation when the HOLD bit is not used involves reading the same digit twice and comparing the read values. This is to avoid the problem of reading unstable data that would occur if the data was read while the RTC was incrementing the count.

#### 3. Write to 30-second ADJ bit