## 40V, 2A Synchronous Buck-Boost DC/DC Converter

### **FEATURES**

- Wide V<sub>IN</sub> Range: 2.7V to 40VWide V<sub>OUT</sub> Range: 2.7V to 40V

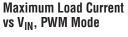

- 1A Output Current for V<sub>IN</sub> ≥ 3.6V, V<sub>OUT</sub> = 5V

2A Output Current in Step-Down Operation

- ZA Output Gurrent in Step-Down for V<sub>IN</sub> ≥ 6V

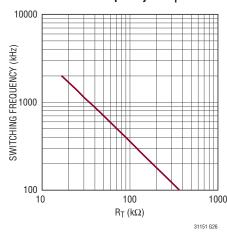

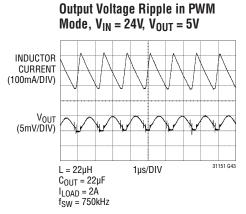

- Programmable Frequency: 100kHz to 2MHz

- Synchronizable Up to 2MHz with an External Clock

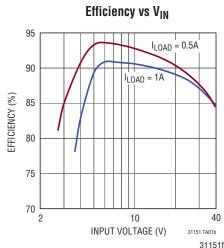

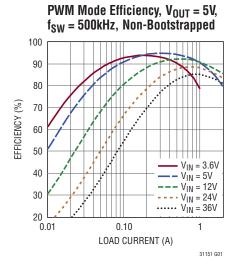

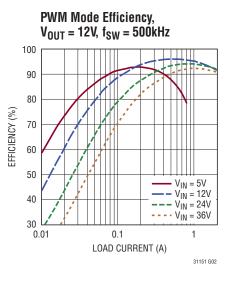

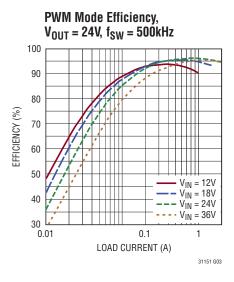

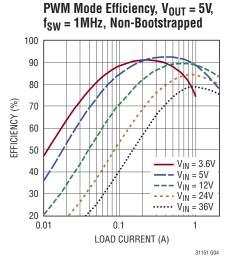

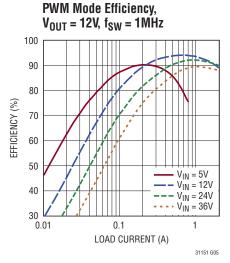

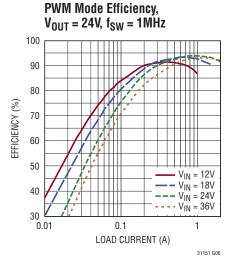

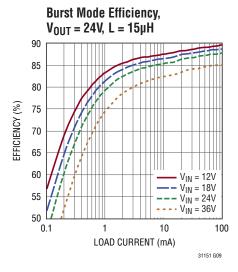

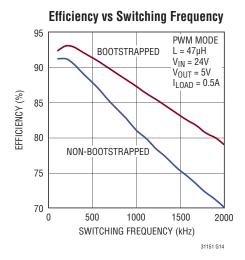

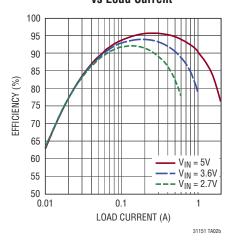

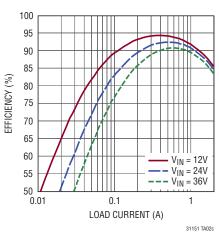

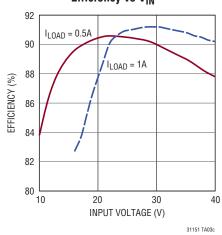

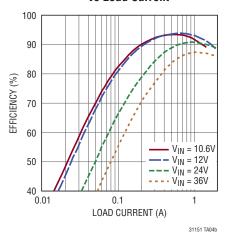

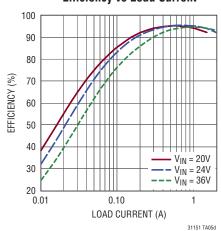

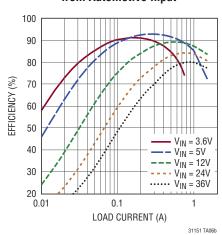

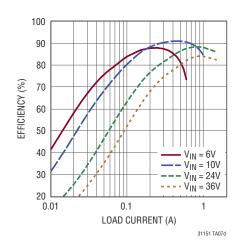

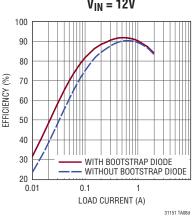

- Up to 95% Efficiency

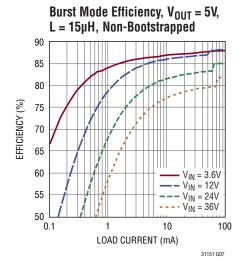

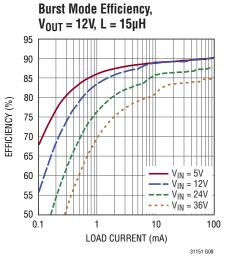

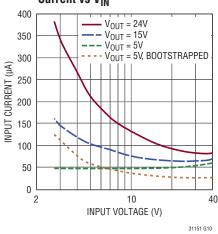

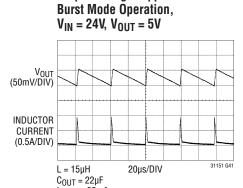

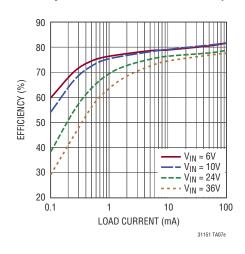

- 30µA No-Load Quiescent Current in Burst Mode® Operation

- Ultralow Noise Buck-Boost PWM

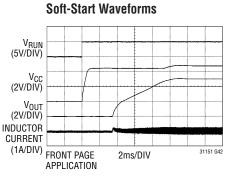

- Internal Soft-Start

- 3µA Supply Current in Shutdown

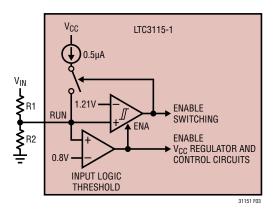

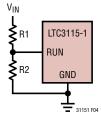

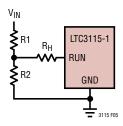

- Programmable Input Undervoltage Lockout

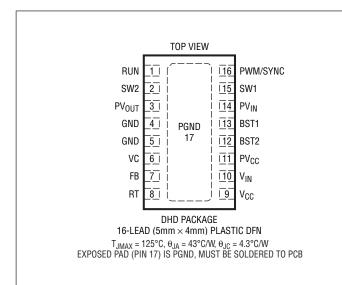

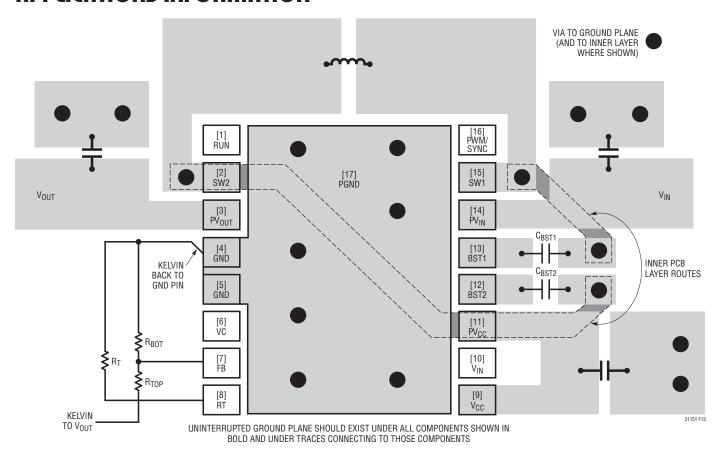

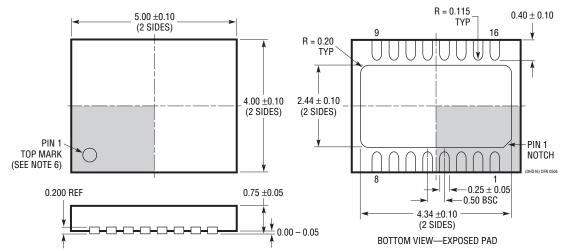

- Small 4mm × 5mm × 0.75mm DFN Package

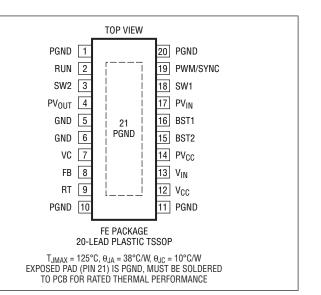

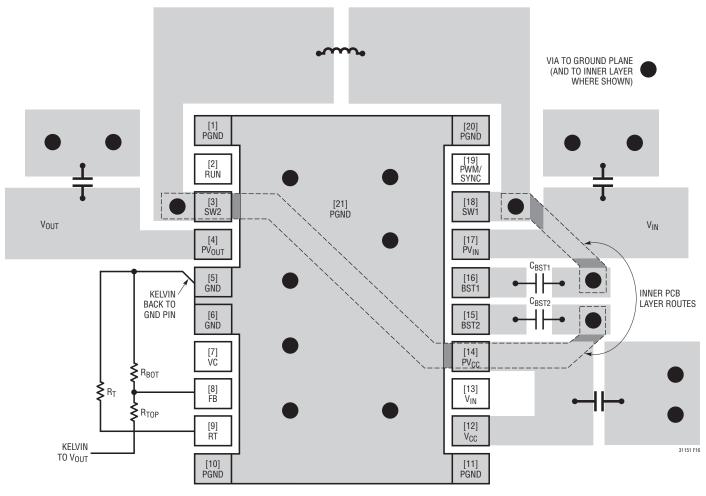

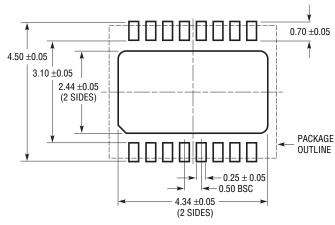

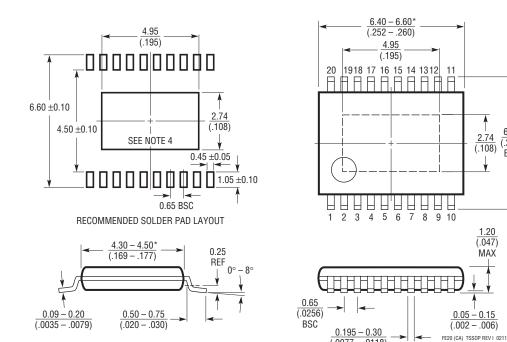

- Thermally Enhanced 20-Lead TSSOP Package

## **APPLICATIONS**

- 24V/28V Industrial Applications

- Automotive Power Systems

- Telecom, Servers and Networking Equipment

- FireWire Regulator

- Multiple Power Source Supplies

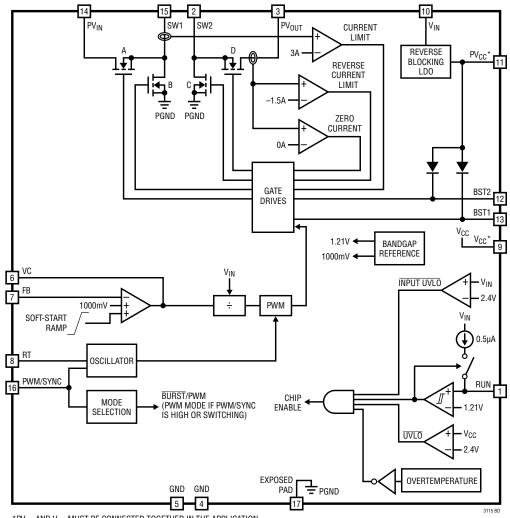

### DESCRIPTION

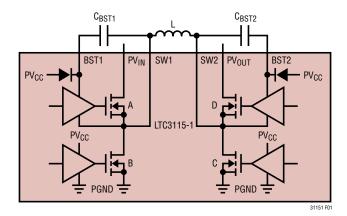

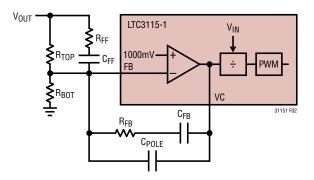

The LTC®3115-1 is a high voltage monolithic synchronous buck-boost DC/DC converter. Its wide 2.7V to 40V input and output voltage ranges make it well suited to a wide variety of automotive and industrial applications. A proprietary low noise switching algorithm optimizes efficiency with input voltages that are above, below or even equal to the output voltage and ensures seamless transitions between operational modes.

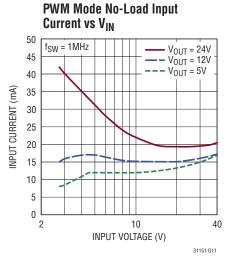

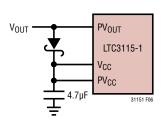

Programmable frequency PWM mode operation provides low noise, high efficiency operation and the ability to synchronize switching to an external clock. Switching frequencies up to 2MHz are supported to allow use of small valued inductors for miniaturization of the application circuit. Pin selectable Burst Mode operation reduces standby current and improves light load efficiency which combined with a 3µA shutdown current make the LTC3115-1 ideally suited for battery-powered applications. Additional features include output disconnect in shutdown, short-circuit protection and internal soft-start. The LTC3115-1 is available in thermally enhanced 16-lead 4mm  $\times$  5mm  $\times$  0.75mm DFN and 20-lead TSSOP packages.

**Δ7**, LT, LTC, LTM, Burst Mode, LTspice, Linear Technology and the Linear logo are registered trademarks and No R<sub>SENSE</sub> is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 6404251, 6166527 and others pending.

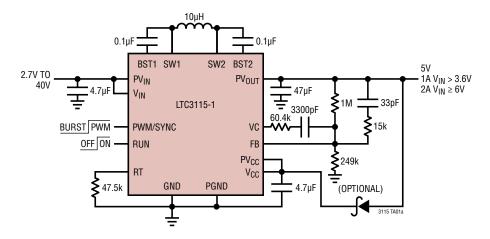

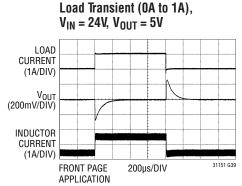

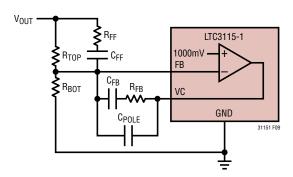

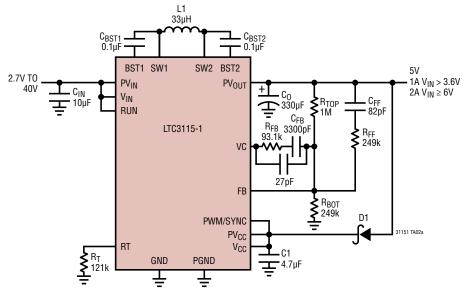

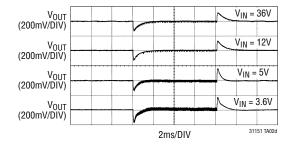

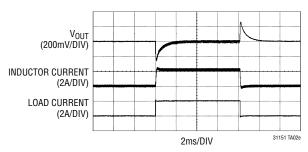

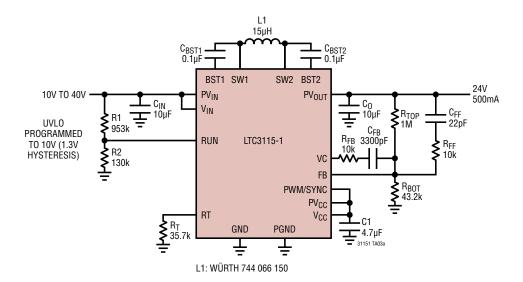

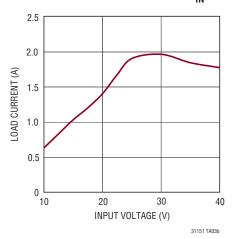

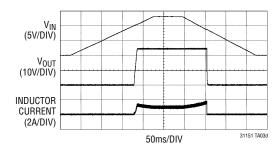

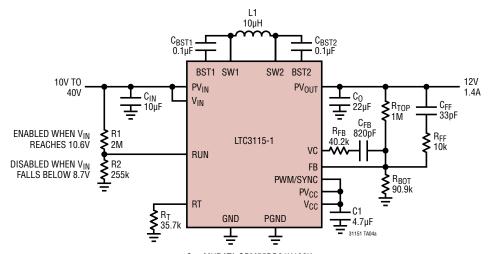

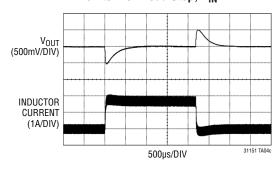

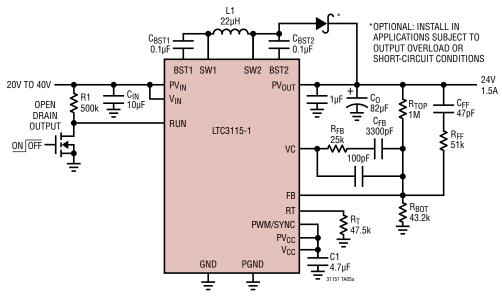

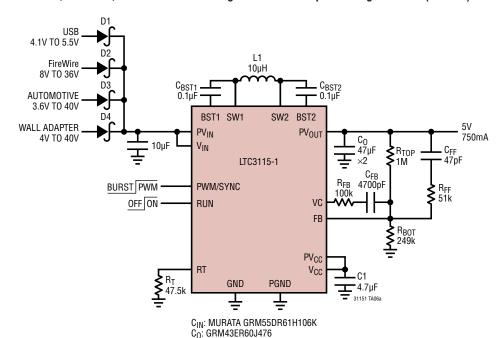

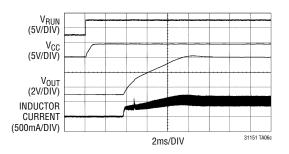

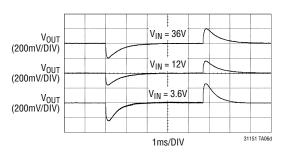

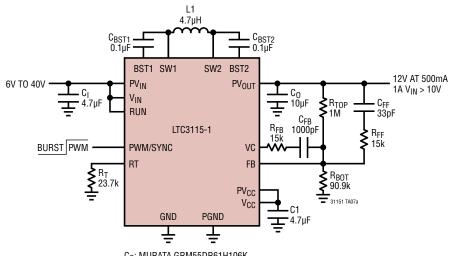

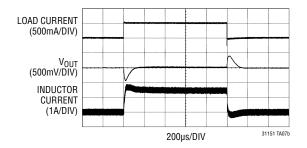

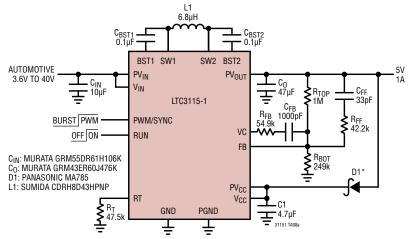

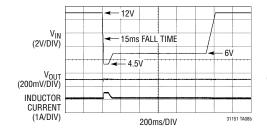

## TYPICAL APPLICATION

## **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| 0.3V to 45V                         |

|-------------------------------------|

| 0.01/1. (D)/ 0.01/1                 |

| $-0.3V$ to $(PV_{IN} + 0.3V)$       |

| $-1.5V$ to $(PV_{IN} + 1.5V)$       |

|                                     |

| -0.3V to (PV <sub>OUT</sub> + 0.3V) |

| –1.5V to (PV <sub>OUT</sub> + 1.5V) |

| $-0.3V$ to $(V_{IN} + 0.3V)$        |

|                                     |

| $V_{BST1}$ $V_{SW1} - 0.3V$ to $V_{SW1} + 6V$     |

|---------------------------------------------------|

| $V_{BST2}$ $V_{SW2} - 0.3V$ to $V_{SW2} + 6V$     |

| Voltage, All Other Pins0.3V to 6V                 |

| Operating Junction Temperature Range (Notes 2, 4) |

| LTC3115E-1/LTC3115I-140°C to 125°C                |

| Storage Temperature Range65°C to 150°C            |

| Lead Temperature (Soldering, 10 sec)              |

| FE300°C                                           |

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|---------------------|---------------|---------------------------------|-------------------|

| LTC3115EDHD-1#PBF | LTC3115EDHD-1#TRPBF | 31151         | 16-Lead (5mm × 4mm) Plastic DFN | -40°C to 125°C    |

| LTC3115IDHD-1#PBF | LTC3115IDHD-1#TRPBF | 31151         | 16-Lead (5mm × 4mm) Plastic DFN | -40°C to 125°C    |

| LTC3115EFE-1#PBF  | LTC3115EFE-1#TRPBF  | LTC3115FE-1   | 20-Lead Plastic TSSOP           | -40°C to 125°C    |

| LTC3115IFE-1#PBF  | LTC3115IFE-1#TRPBF  | LTC3115FE-1   | 20-Lead Plastic TSSOP           | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are for $T_A = 25^{\circ}C$ (Note 2). $V_{IN} = 24V$ , $V_{OUT} = 5V$ , unless otherwise noted.

| Input Operating Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PARAMETER                                       | CONDITIONS                                                      |   | MIN  | TYP  | MAX  | UNITS                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------|---|------|------|------|----------------------|

| Input Undervoltage Lockout Threshold   V <sub>IN</sub> Falling   V <sub>IN</sub> Rising   V <sub>IN</sub> Ri | Input Operating Voltage                         |                                                                 | • | 2.7  |      | 40   | V                    |

| Vim Rising (°C to 125°C)         26         2.8 b (2.725)         V V (NR) Rising (°C to 125°C)         26         2.725         V V (NR) Rising (°C to 125°C)         V (December 100)         mV         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Output Operating Voltage                        |                                                                 | • | 2.7  |      | 40   |                      |

| No.   Rising (0°C to 125°C)   2.725   V   No.   No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Input Undervoltage Lockout Threshold            |                                                                 | • |      |      |      |                      |

| V <sub>CC</sub> Undervoltage Lockout Threshold         V <sub>CC</sub> Falling         ■ 2.4         2.6         V           V <sub>CC</sub> Undervoltage Lockout Hysteresis         200         mV           Input Current in Burst Mode Operation         V <sub>RUN</sub> = 0V         3         10         µA           Input Quiescent Current in Burst Mode Operation         V <sub>FB</sub> = 1.1V (Not Switching)         50         µA           Oscillator Frequency         • 100         2000         kHz           Oscillator Operating Frequency         • 100         2000         kHz           PWMMSYNC Clock Input Frequency         • 100         2000         kHz           PWMSYNC Clock Input Frequency         • 0.5         1.0         1.5         V           Soft-Start Duration         9         ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                 | V <sub>IN</sub> Rising<br>V <sub>IN</sub> Rising (0°C to 125°C) | • |      | 2.6  |      |                      |

| VCC Undervoltage Lockout Hysteresis         200         mV           Input Current in Shutdown         VR, Wn = 0V         3         10         µA           Input Quiescent Current in Burst Mode Operation         VFB = 1.1V (Not Switching)         50         µA           Oscillator Operating Frequency         PMM/SYNC Clock Input Frequency         • 100         2000         kHz           Dewill SyNC Clock Input Logic Threshold         • 0.5         1.0         1.5         V           Feedback Voltage         • 977         1000         1017         mV           Feedback Voltage Line Regulation         V <sub>N</sub> = 2.7V to 40V         0.1         50         nA           RUN Pin Input Current         1         50         nA           RUN Pin Input Logic Threshold         • 0.3         0.8         1.1         V           RUN Pin Hysteresis Current         1         50         nA           RUN Pin Hysteresis Voltage         100         mV         mV           Inductor Current Limit         (Note 3)         1.5         A           Reverse Inductor Current Limit         (Note 3)         1.5         A           Maximum Duty Cycle         Percentage of Period SW2 is Low in Boost Mode, R <sub>T</sub> = 35.7k (Note 5)         90         95         %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input Undervoltage Lockout Hysteresis           |                                                                 |   |      | 100  |      | mV                   |

| Input Current in Shutdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>CC</sub> Undervoltage Lockout Threshold  | V <sub>CC</sub> Falling                                         | • |      | 2.4  | 2.6  | V                    |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>CC</sub> Undervoltage Lockout Hysteresis |                                                                 |   |      | 200  |      | mV                   |

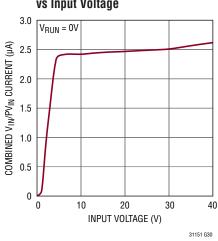

| Oscillator Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Input Current in Shutdown                       | V <sub>RUN</sub> = 0V                                           |   |      | 3    | 10   | μΑ                   |

| Oscillator Operating Frequency   ● 100   2000   kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Input Quiescent Current in Burst Mode Operation | V <sub>FB</sub> = 1.1V (Not Switching)                          |   |      | 50   |      | μΑ                   |

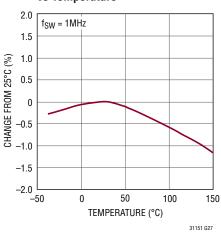

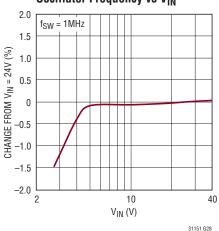

| PWM/SYNC Clock Input Logic Threshold         100         2000         kHz           PWM/SYNC Input Logic Threshold         • 0.5         1.0         1.5         V           Soft-Start Duration         9         ms           Feedback Voltage         • 977         1000         1017         mV           Feedback Voltage Line Regulation         V <sub>IN</sub> = 2.7V to 40V         0.1         %           Feedback Voltage Line Regulation         V <sub>IN</sub> = 2.7V to 40V         0.3         0.8         1.1         50         nA           RUN Pin Input Current         1         50         nA         RUN Pin Input Logic Threshold         V <sub>RUN</sub> Rising         1.16         1.21         1.26         V           RUN Pin Hysteresis Current         500         nA         nA         NUN Pin Hysteresis Voltage         1.16         1.21         1.26         V         NO         n         N         NUN Pin Hysteresis Voltage         1.00         mV         mV         mV         mV         NUN Pin Hysteresis Voltage         1.16         1.21         1.26         V         N         N         N         A         8         1.16         1.21         1.26         V         N         N         N         N         N         N         N </td <td>Oscillator Frequency</td> <td>R<sub>T</sub> = 35.7k</td> <td>•</td> <td>900</td> <td>1000</td> <td>1100</td> <td>kHz</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Oscillator Frequency                            | R <sub>T</sub> = 35.7k                                          | • | 900  | 1000 | 1100 | kHz                  |

| PWM/SYNC Input Logic Threshold         ● 0.5         1.0         1.5         V           Soft-Start Duration         9         mS           Feedback Voltage         • 977         1000         1017         mV           Feedback Voltage Line Regulation         V <sub>IN</sub> = 2.7V to 40V         0.1         %           Feedback Voltage Line Regulation         V <sub>IN</sub> = 2.7V to 40V         0.3         0.8         1.1         V           RUN Pin Input Logic Threshold         V <sub>RUN</sub> Rising         0.16         1.21         1.26         V           RUN Pin Hysteresis Current         500         nA           RUN Pin Hysteresis Current         500         nA           RUN Pin Hysteresis Current         500         mV           Inductor Current Limit         (Note 3)         1.0         3.7         A           Reverse Inductor Current Limit         (Note 3)         1.5         A           Burst Mode Inductor Current Limit         (Note 3)         1.5         A           Maximum Duty Cycle         Percentage of Period SW2 is Low in Boost Mode, R <sub>T</sub> = 35.7 k (Note 5)         90         95         %           Minimum Duty Cycle         Percentage of Period SW2 is High in Buck Mode, R <sub>T</sub> = 35.7 k (Note 5)         0.65         1.0         1.3         A <td>Oscillator Operating Frequency</td> <td></td> <td>•</td> <td>100</td> <td></td> <td>2000</td> <td>kHz</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Oscillator Operating Frequency                  |                                                                 | • | 100  |      | 2000 | kHz                  |

| Soft-Start Duration   9 ms   Feedback Voltage   0 977 1000 1017 mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PWM/SYNC Clock Input Frequency                  |                                                                 | • | 100  |      | 2000 | kHz                  |

| Feedback Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PWM/SYNC Input Logic Threshold                  |                                                                 | • | 0.5  | 1.0  | 1.5  | V                    |

| Feedback Voltage Line Regulation         V <sub>IN</sub> = 2.7V to 40V         0.1         %           Feedback Pin Input Current         1         50         nA           RUN Pin Input Logic Threshold         •         0.3         0.8         1.1         V           RUN Pin Hystereshold         V <sub>RUN</sub> Rising         •         1.16         1.21         1.26         V           RUN Pin Hysteresis Current         500         nA           RUN Pin Hysteresis Voltage         100         mV           Inductor Current Limit         (Note 3)         2.4         3.0         3.7         A           Reverse Inductor Current Limit         (Note 3)         1.5         A           Burst Mode Inductor Current Limit         (Note 3)         0.65         1.0         1.35         A           Maximum Duty Cycle         Percentage of Period SW2 is Low in Boost Mode, R <sub>T</sub> = 35.7k (Note 5)         90         95         %           Minimum Duty Cycle         Percentage of Period SW1 is High in Buck Mode, R <sub>T</sub> = 35.7k (Note 5)         0         %           SW1, SW2 Minimum Low Time         R <sub>T</sub> = 35.7k (Note 5)         100         ns           N-Channel Switch Resistance         Switch A (From PV <sub>IN</sub> to SW1) Switch D(From PV <sub>IN</sub> to SW1)         150         mΩ           Swit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Soft-Start Duration                             |                                                                 |   |      | 9    |      | ms                   |

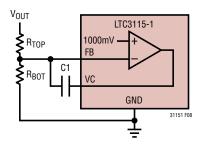

| Feedback Pin Input Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Feedback Voltage                                |                                                                 | • | 977  | 1000 | 1017 | mV                   |

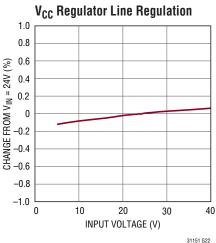

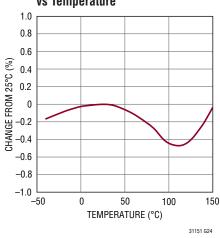

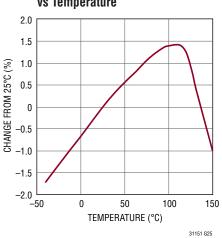

| RUN Pin Input Logic Threshold   VRUN Rising   0.3 0.8 1.1 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Feedback Voltage Line Regulation                | V <sub>IN</sub> = 2.7V to 40V                                   |   |      | 0.1  |      | %                    |

| RUN Pin Comparator Threshold         V <sub>RUN</sub> Rising         ■ 1.16         1.21         1.26         V           RUN Pin Hysteresis Current         500         nA           RUN Pin Hysteresis Voltage         100         mV           Inductor Current Limit         (Note 3)         • 2.4         3.0         3.7         A           Reverse Inductor Current Limit         (Note 3)         1.5         A           Burst Mode Inductor Current Limit         (Note 3)         0.65         1.0         1.35         A           Maximum Duty Cycle         Percentage of Period SW2 is Low in Boost Mode, R <sub>T</sub> = 35.7k (Note 5)         • 90         95         %           Minimum Duty Cycle         Percentage of Period SW1 is High in Buck Mode, R <sub>T</sub> = 35.7k (Note 5)         • 90         95         %           SW1, SW2 Minimum Low Time         R₁ = 35.7k (Note 5)         100         ns           N-Channel Switch Resistance         Switch A (From PV <sub>IN</sub> to SW1)         150         mΩ           Switch Resistance         Switch B (From SW1 to PGND)         150         mΩ           Switch B (From SW2 to PGND)         150         mΩ           Switch B (From SW2 to PGND)         150         mΩ           Switch D (From PV <sub>OUT</sub> to SW2)         150         mΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Feedback Pin Input Current                      |                                                                 |   |      | 1    | 50   | nA                   |

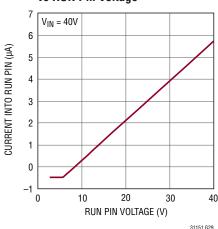

| RUN Pin Hysteresis Current         500         nA           RUN Pin Hysteresis Voltage         100         mV           Inductor Current Limit         (Note 3)         2.4         3.0         3.7         A           Reverse Inductor Current Limit         (Note 3)         0.65         1.0         1.35         A           Burst Mode Inductor Current Limit         (Note 3)         0.65         1.0         1.35         A           Maximum Duty Cycle         Percentage of Period SW2 is Low in Boost Mode, R <sub>T</sub> = 35.7k (Note 5)         90         95         %           Minimum Duty Cycle         Percentage of Period SW1 is High in Buck Mode, R <sub>T</sub> = 35.7k (Note 5)         0         %         %           SW1, SW2 Minimum Low Time         R <sub>T</sub> = 35.7k (Note 5)         100         ns         ns           N-Channel Switch Resistance         Switch A (From PV <sub>IN</sub> to SW1)         150         mΩ           Switch B (From SW1 to PGND)         150         mΩ           Switch D (From PV <sub>OUT</sub> to SW2)         150         mΩ           N-Channel Switch Leakage         PV <sub>IN</sub> = PV <sub>OUT</sub> = 40V         0.1         10         μA           PV <sub>CC</sub> /V <sub>CC</sub> External Forcing Voltage         I <sub>VCC</sub> = 1mA         4.33         4.45         4.58         V           V <sub>CC</sub> Load Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RUN Pin Input Logic Threshold                   |                                                                 | • | 0.3  | 0.8  | 1.1  | V                    |

| RUN Pin Hysteresis Voltage         (Note 3)         ■ 2.4         3.0         3.7         A           Reverse Inductor Current Limit         Current into PV <sub>OUT</sub> (Note 3)         1.5         A           Burst Mode Inductor Current Limit         (Note 3)         0.65         1.0         1.35         A           Maximum Duty Cycle         Percentage of Period SW2 is Low in Boost Mode, R <sub>T</sub> = 35.7k (Note 5)         ● 90         95         %           Minimum Duty Cycle         Percentage of Period SW1 is High in Buck Mode, R <sub>T</sub> = 35.7k (Note 5)         ■ 0         %           SW1, SW2 Minimum Low Time         R <sub>T</sub> = 35.7k (Note 5)         100         ns           N-Channel Switch Resistance         Switch A (From PV <sub>IN</sub> to SW1)         150         mΩ           Switch B (From SW1 to PGND)         150         mΩ           Switch D (From PV <sub>OUT</sub> to SW2)         150         mΩ           N-Channel Switch Leakage         PV <sub>IN</sub> = PV <sub>OUT</sub> = 40V         0.1         10         μA           PV <sub>CC</sub> /V <sub>CC</sub> External Forcing Voltage         4.58         5.5         V           V <sub>CC</sub> Regulation Voltage         I <sub>VCC</sub> = 1mA         4.33         4.45         4.58         V           V <sub>CC</sub> Line Regulation         I <sub>VCC</sub> = 1mA, V <sub>IN</sub> = 5V to 40V         0.5         50         110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RUN Pin Comparator Threshold                    | V <sub>RUN</sub> Rising                                         | • | 1.16 | 1.21 | 1.26 | V                    |

| $ \begin{array}{ c c c c } \hline \text{Inductor Current Limit} & (\text{Note 3}) & \bullet & 2.4 & 3.0 & 3.7 & A \\ \hline \text{Reverse Inductor Current Limit} & \text{Current into PV}_{\text{OUT}} \text{ (Note 3}) & 1.5 & A \\ \hline \text{Burst Mode Inductor Current Limit} & (\text{Note 3}) & 0.65 & 1.0 & 1.35 & A \\ \hline \text{Maximum Duty Cycle} & \text{Percentage of Period SW2 is Low in Boost Mode,} & 90 & 95 & \% \\ \hline \text{Minimum Duty Cycle} & \text{Percentage of Period SW1 is High in Buck Mode,} & 90 & 95 & \% \\ \hline \text{Minimum Low Time} & \text{Percentage of Period SW1 is High in Buck Mode,} & 0.65 & 1.0 & 1.35 & A \\ \hline \text{Minimum Low Time} & \text{Percentage of Period SW1 is High in Buck Mode,} & 0.65 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1.0 & 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RUN Pin Hysteresis Current                      |                                                                 |   |      | 500  |      | nA                   |